# RAIO RA8870

文字 / 图形

TFT LCD 控制器

基本规格书

Version 1.1

February 7, 2013

RAiO Technology Inc.

©Copyright RAiO Technology Inc, 2010, 2011, 2012, 2013

## 1. 简介

RA8870 是一个文字与绘图模式的液晶显示(TFT-LCD)控制器,可结合文字或 2D 图形应用,支持最大到 640\*480 点分辨率的中小尺寸数字或模拟 TFT 屏。RA8870 内建内存能支持 65K 色的 320\*240 单图层显示; 4K 色的 320\*240 双图层显示; 或者是 4K 色的 320\*480、640\*240 的单图层显示,若外接内存最高可支持到 65K 色的 640\*480 单图层显示。

RA8870 内建 CGROM 能显示国际标准的 ISO 8859-1/2/3/4 字型,包含 256\*4 个可显示大部份使用于英语系和欧洲国家的半型字字母及符号。在图形的使用上,RA8870 支援一 2D 的 BTE 引擎(Block Transfer Engine),此 BTE 兼容于一般通用的 2D BitBLT 的功能,可用于处理大量图形数据转换。同时 RA8870 也内建几何图形加速引擎(Geometric Speed-up Engine),提供用户可以透过简单的设定轻松的画出直线、矩形和圆形的几何图形形状。除此之外,RA8870 还包括一些强大的图形处理功能,如画面旋转功能、卷动功能、图形 Pattern、双层混合显示和文字放大等等,这些功能将可节省用户在中小尺寸 TFT 屏应用的开发时间,并且提升 MCU 软件的执行效率。

RA8870 提供低成本的 8-bit 或 16-bit 8080 / 6800 MCU 界面,还有一 10-bit 的 4 线或 5 线式触摸屏控制器,另外 2 组的脉宽调制(PWM)可用于调整 TFT 屏背光或其它应用。相对于其它的解决方案,RA8870 是一个功能强大和廉价的彩色 TFT 控制器,可以让以往单色 STN 屏的应用顺利、快速、轻易的转成 TFT 屏的应用,解决设计者在软硬件开发上的疑虑,同时达成低成本、高效能的系统方案。

## 2. 特性

- ◆ 支持文字和绘图两种混和显示模式

- ◆ 时钟(Clock)来源:外部晶振配合内部PLL

- ◆ 色彩深度: 256/4K/65K 色

- ◆ 支援 MCU 界面: 8-bit 或 16-bit 数据总线的 8080/6800 系列

- ◆ 内建 DDRAM 内存: 230KB

- ◆ 内建 10KB 字型 ROM (8\*16 dots) 及支持标准 ISO8859-1/2/3/4

- ◆ 支持 GB-2312 及 BIG-5 编码的外部 16\*16 dots 字型 ROM

- ◆ 外部 DDRAM 最大可支持到 512KB\*16

- ◆ 支持 1 倍到 4 倍字型放大(垂直和水平)

- ◆ 支持 8/12/16-bit Generic RGB TFT 界面或模 拟 TFT 屏界面。

- ◆ 内建 TCON 可支持大部分模拟屏

- ◆ 支持90度、180度、270度文字旋转显示功能

- ◆ 文字垂直旋转模式功能

- ◆ 支持水平和垂直区域卷动

- ◆ 内建 2D Block Transfer Engine (BTE) 功能

- ◆ 内建几何图形加速绘图引擎

- ◆ 提供文字光标功能

- ◆ 提供 32\*32 pixel 的图形光标功能

- ◆ 支援 TFT 屏大小:双图层:最大 320\*240 点分辨率(使用内建内存)

单图层: 最大 640\*480 点分辨率

- ◆ 支持 256 个用户自订 8\*16 字符符号

- ◆ 支持 32 个用户自建 8\*8 pixel 图形 Pattern

- ◆ 内建 2 组脉冲宽度调制 (PWM) 提供 LCD 背 光的调节或其它用途

- ◆ 内建4或5线电阻式触摸屏控制器

- ◆ 提供 6 个 GPIO (GPIO0~5)

- ◆ 电源操作范围: 3.0V~3.6V

- ◆ 封装: TQFP-128pin.

## 3. 系统方块图

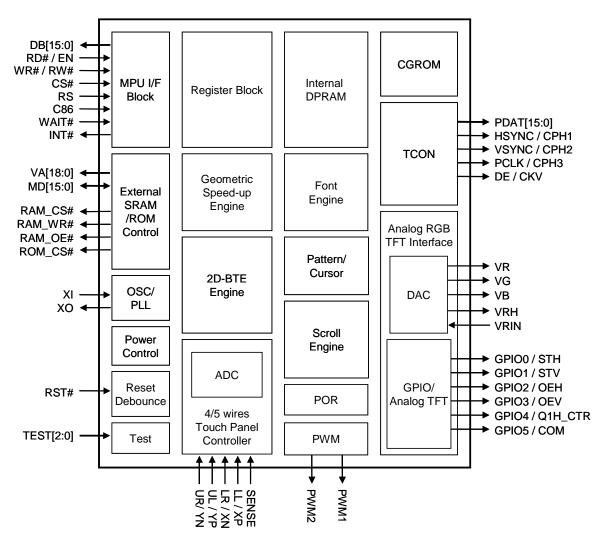

图 3-1: 内部方块图

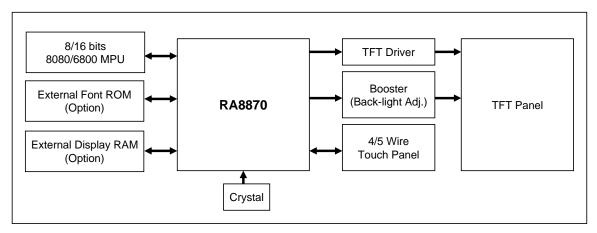

图 3-2: 系统方块图

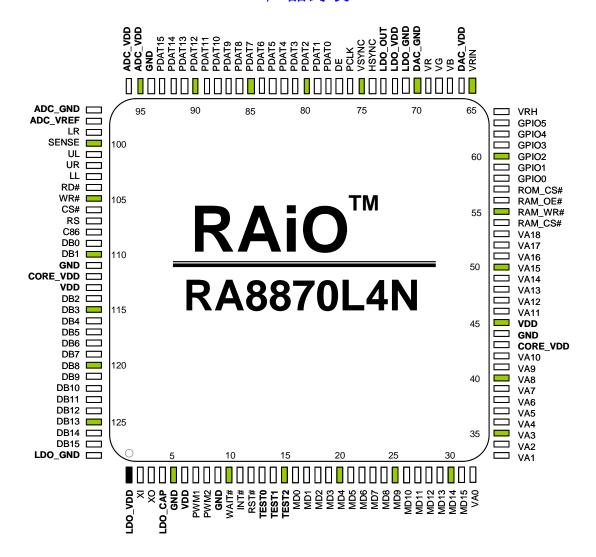

## 4. 管脚定义

## 4-1 MCU界面

| 管 脚 名 称   | I/O | Pin#                      |                                                                                 | ~              | <b>からない かくしょう かいまた かいまた かいまた かいまた かいまた かいまた かいまた かいまた</b> |        |

|-----------|-----|---------------------------|---------------------------------------------------------------------------------|----------------|-----------------------------------------------------------|--------|

|           |     | 109,                      | 数据总线(Data B                                                                     | us)            |                                                           |        |

| DB[15:0]  | 10  | 110,<br>114~<br>127       | │<br>负责 RA8870 及微                                                               | 处理器(MC         | CU)之间的数据传送与接收。                                            |        |

|           | 10  |                           | 当于使用 8-bit 数:                                                                   | 居总线模式          | 下, <b>DB[15:8]</b> 当保持当保持接下                               | 拉/上拉   |

|           |     |                           | 电阻到 GND 或 VD                                                                    | D.             |                                                           |        |

|           |     |                           | 致能 / 读取控制信                                                                      | 号(Enable       | e / Read Enable)                                          |        |

| RD# / EN  | ١,  | 104                       | 当 MCU 为 8080 系                                                                  | <b>≶列时,此</b> 脚 | 〕为数据读取信号(RD#),于值                                          | 氏电位动   |

| ND#/ EN   | '   |                           | 作。                                                                              |                |                                                           |        |

|           |     |                           | 当 MCU 为 6800 豸                                                                  | <b>≶列时,此</b> 脚 | 为致能信号(EN),于高电位:                                           | 动作。    |

|           |     |                           | 写入 / 读-写控制信                                                                     | 号(Write        | / Read-Write )                                            |        |

|           |     |                           | 当 MCU 为 8080 系                                                                  | <b>≶列时,此脚</b>  | 为数据写入信号(WR#),于值                                           | 氐电位动   |

| WR# / RW# | ı   | 105                       | 作。                                                                              |                |                                                           |        |

|           |     |                           | 当 MCU 为 6800 矛                                                                  | <b>≶列时,此脚</b>  | 为数据读取 / 写入信号 (RW#)                                        | ),于高   |

|           |     |                           | 电位时表示读取动                                                                        | 作,于低电位         | 立时表示写入动作。                                                 |        |

| CS#       | ı   | 106                       | 芯片选取控制信号                                                                        | (Chip Sele     | ect Input)                                                |        |

|           |     |                           | Low 动作的芯片选                                                                      | 取输入。           |                                                           |        |

|           |     |                           | 指令 / 数据选择控                                                                      | 制信号(Co         | ommand / Data Select Input)                               |        |

|           |     |                           |                                                                                 |                | 期或数据周期。当 RS = 0 时,R                                       |        |

|           |     |                           | 数据读取或写入周期。当 RS = 1 时,RA8870 为状态(Status)读取或指令写入周期,当于 8080 接口时,通常此管脚和微处理器的 A0 相接。 |                |                                                           |        |

|           |     |                           | 指令与人向期,当                                                                        | ナ 8080 接口      | 1时,                                                       | AU 相接。 |

| RS        | I   | 107                       | RS                                                                              | WR#            | 存取周期                                                      |        |

|           |     |                           | 0                                                                               | 0              | 数据写入(Data Write)                                          |        |

|           |     |                           | 0                                                                               | 1              | 数据读取(Data Read)                                           |        |

|           |     |                           | 1                                                                               | 0              | 指令写入(CMD Write)                                           |        |

|           |     |                           | 1                                                                               | 1              | 状态读取(Status Read)                                         |        |

|           |     |                           | MCU 界面选择                                                                        |                |                                                           |        |

| C86       | ı   | 108                       | 0 : Intel 8080 系列 MCU 接口。                                                       |                |                                                           |        |

|           |     |                           | 1 : Motorola 6800                                                               | 系列 MCU 括       | 妾口。                                                       |        |

| INT#      | 0   | 11                        | 中断信号(Interru                                                                    | pt Signal O    | output)                                                   |        |

|           | Ŭ   | 用以发出 RA8870 内部的中断状况给 MCU。 |                                                                                 |                |                                                           |        |

|           | 0   | 10                        | 等待信号(Wait S                                                                     | ignal Outpu    | ut)                                                       |        |

| WAIT#     |     |                           | 用以反应 RA8870                                                                     | 内部的执行          | 产使用状况。当 WAIT# 为 Low                                       | 时表示    |

|           |     |                           | RA8870 正处于忙                                                                     | 录状态, 无法        | 接受来自 MCU 指令。把此管脚                                          | 接到 I/O |

|           |     |                           | 管脚时,它能被使                                                                        | 用于轮询机制         | 制(Polling)来监控内部的状况                                        | 0      |

## 4-2 LCD屏界面

| 管脚名称               | I/O | Pin#  | 管 脚 说 明                                                                                                            |

|--------------------|-----|-------|--------------------------------------------------------------------------------------------------------------------|

| PDAT[15:0]         | 0   | 78~93 | LCD 屏数据总线<br>数据总线输出端接到 TFT LCD 屏的 Driver IC。用户必须将这些数据总<br>线接到对应的 TFT LCD 屏的相对信号。                                   |

| HSYNC / CPH1       | 0   | 74    | HSYNC Pulse / CPH1 当使用 Generic TFT(数字 TFT 屏)时,此管脚定义为 HSYNC。<br>当使用模拟 TFT 时,此管脚定义为 CPH1。                            |

| VSYNC / CPH2       | 0   | 75    | VSYNC Pulse / CPH2<br>当使用 Generic TFT 时,此管脚定义为 VSYNC。<br>当使用模拟 TFT 时,此管脚定义为 CPH2。                                  |

| PCLK / CPH3        | 0   | 76    | Pixel Clock / CPH3         当使用 Generic TFT 时,此管脚定义为 PCLK。         当使用模拟 TFT 时,此管脚定义为 CPH3。                         |

| DE / CKV           | 0   | 77    | Data Enable / CKV<br>当使用 Generic TFT 时,此管脚定义为 DE。<br>当使用模拟 TFT 时,此管脚定义为 CKV。                                       |

| GPIO0 / STH        | Ю   | 58    | 通用 GPIO 信号 0 / STH<br>当使用 Generic TFT 时,此管脚定义为一通用 GPIO 信号(GPIO_0),<br>用户可由寄存器设定之。<br>当使用模拟 TFT 时,此管脚定义为 STH。       |

| GPIO1 / STV        | Ю   | 59    | 通用 GPIO 信号 1 / STV<br>当使用 Generic TFT 时,此管脚定义为一通用 GPIO 信号(GPIO_1)。<br>当使用模拟 TFT 时,此管脚定义为 STV。                      |

| GPIO2 / OEH        | Ю   | 60    | 通用 GPIO 信号 2 / OEH<br>当使用 Generic TFT 时,此管脚定义为一通用 GPIO 信号(GPIO_2)。<br>当使用模拟 TFT 时,此管脚定义为 OEH。                      |

| GPIO3 / OEV        | Ю   | 61    | 通用 GPIO 信号 3 / OEV<br>当使用 Generic TFT 时,此管脚定义为一通用 GPIO 信号(GPIO_3)。<br>当使用模拟 TFT 时,此管脚定义为 OEV。                      |

| GPIO4 /<br>Q1H_CTR | Ю   | 62    | <b>通用 GPIO 信号 4 / Q1H_CTR</b> 当使用 Generic TFT 时,此管脚定义为一通用 GPIO 信号(GPIO_4)。<br>当使用模拟 TFT 时,此管脚定义为 Q1H_CTR,用来控制 Q1H。 |

| 管脚名称        | I/O | Pin# | 管 脚 说 明                                      |

|-------------|-----|------|----------------------------------------------|

| GPIO5 / COM |     | 63   | 通用 GPIO 信号 5 / COM                           |

|             | Ю   |      | 当使用 Generic TFT 时,此管脚定义为一通用 GPIO 信号(GPIO_5)。 |

|             |     |      | 当使用模拟 TFT 时,此管脚定义为 COM,用来控制 VCOM。            |

| VR          | 0   | 69   | 模拟 Red 输出                                    |

|             |     |      | 此信号接到模拟 TFT 屏的驱动器 Red Data 输入端。              |

| VG          | 0   | 68   | 模拟 Green 输出                                  |

| VG          |     |      | 此信号接到模拟 TFT 屏的驱动器 Green Data 输入端。            |

| VB          | 0   | 67   | 模拟 Blue 输出                                   |

|             |     |      | 此信号接到模拟 TFT 屏的驱动器 Blue Data 输入端。             |

## 4-3 触摸屏与脉宽调制界面

| 管脚名称    | I/O | Pin#    | 管 脚 说 明                                 |

|---------|-----|---------|-----------------------------------------|

| UR / YN | Α   | 102     | 触摸屏控制信号                                 |

|         |     |         | 当使用 5 线式触摸屏,此管脚定义为 UR 输出信号。             |

|         |     |         | 当使用 4 线式触摸屏,此管脚定义为 YN 信号。               |

|         | Α   | 101     | 触摸屏控制信号                                 |

| UL/YP   |     |         | 当使用 5 线式触摸屏,此管脚定义为 UL 输出信号。             |

| OL/ IP  |     |         | 当使用 4 线式触摸屏,此管脚定义为 YP 信号。               |

|         |     |         | 当使用触摸屏扫瞄功能时,请在此脚位外接 100Kohm pull-up 电阻。 |

|         | А   | 99      | 触摸屏控制信号                                 |

| LR / XN |     |         | 当使用 5 线式触摸屏,此管脚定义为 LR 输出信号。             |

|         |     |         | 当使用 4 线式触摸屏,此管脚定义为 XN 信号。               |

|         | А   | 103     | 触摸屏控制信号                                 |

| LL / XP |     |         | 当使用 5 线式触摸屏,此管脚定义为 LL 输出信号。             |

|         |     |         | 当使用 4 线式触摸屏,此管脚定义为 XP 信号。               |

|         | А   | 100     | 5 线式触摸屏 SENSE 信号                        |

| SENSE   |     |         | 当使用 5 线式触摸屏,此管脚定义为 SENSE 输入信号。          |

|         |     |         | 当使用 4 线式触摸屏, 此管脚保持浮接。                   |

| PWM1    | 0   | 7,<br>8 | PWM 输出                                  |

| PWM2    |     |         | PWM 输出,可由寄存器进行程序化输出。                    |

## 4-4 外部内存界面

| 管脚名称        | I/O | Pin#            | 管 脚 说 明                                           |

|-------------|-----|-----------------|---------------------------------------------------|

|             |     | 32~42,<br>46~53 | 外部 RAM / ROM 地址总线(Address Bus)                    |

|             |     |                 | 当使用外部 Font ROM, VA[18:0] 接到 512KB Font ROM 的地址总线。 |

| VA[18:0]    | 0   |                 | 当使用外部 DDRAM(Display RAM), VA[18:0] 接到 RAM 的地址总线。  |

|             |     |                 | 当使用内部 Display RAM 且不使用外部 Font ROM, VA[18:0] 地址总线  |

|             |     |                 | 请保持浮接。                                            |

|             |     | 16~31           | 外部 RAM / ROM 数据总线(Data Bus)                       |

|             |     |                 | 当使用外部 Font ROM, MD[7:0] 为输入信号, MD[15:8] 不被使用。     |

| MD[15:0]    | Ю   |                 | 当使用外部 DDRAM,MD[15:0] 接到 RAM 的数据总线。                |

|             |     |                 | 当使用内部 Display RAM 且不使用外部 Font ROM, MD[15:0] 数据总   |

|             |     |                 | 线建议接到 VDD 以避免 IO 耗电。                              |

| RAM_OE#     | 0   | 56              | RAM 输出致能信号                                        |

| TAM_OL#     |     |                 | 接到外部 DDRAM 的 Data Output Enable 信号。               |

| RAM_WR#     | 0   | 55              | RAM 写入致能信号                                        |

| IVAIN_VVIV# |     |                 | 接到外部 DDRAM 的 Write 信号。                            |

| RAM_CS#     | 0   | 54              | RAM 芯片选择信号(Chip Select)                           |

| INAM_00#    |     |                 | 接到外部 DDRAM 的 Chip Select 信号。                      |

| ROM_CS#     | 0   | 57              | ROM 芯片选择信号                                        |

| KOWI_C3#    |     |                 | 接到外部 Font ROM 的 Chip Select 信号。                   |

## 4-5 时钟与电源

| 管脚名称      | I/O | Pin#  | 管 脚 说 明                                                                                                                 |  |

|-----------|-----|-------|-------------------------------------------------------------------------------------------------------------------------|--|

| ΧI        | ı   | 2     | Crystal 输入管脚<br>此为晶体振荡器的输入端,用来提供内部 PLL 的振荡来源,以便产生<br>RA8870 的内部时钟(Clock)信号。                                             |  |

| хо        | 0   | 3     | Crystal 输出管脚<br>此为晶体振荡器的输出端。                                                                                            |  |

| RST#      | I   | 12    | 复位信号(Reset Signal Input)<br>此管脚为 RA8870 低电位硬件复位输入信号。为了提高抗杂讯的能力,<br>此管脚为 Schmitt-Trigger 输入,当所给的电源准位变低时,能确保此<br>管脚不会被触发。 |  |

| TEST[2:0] | I   | 13~15 | 测试模式输入信号(Test Mode Input)<br>此管脚为测试信号,必须保持接地(GND)。                                                                      |  |

| VRIN      | Α   | 65    | <b>DAC 参考电压输入</b><br>此脚为一参考电压的稳压输入,用来产生 VRH 信号。实际应用外接<br>0.1uF 的电容到地即可。                                                 |  |

|          |   |                               | DAC 参考电压输出                                    |

|----------|---|-------------------------------|-----------------------------------------------|

| VRH      | Α | 64                            | 此脚为内部 DAC 的参考电压输出。实际应用外接 0.2uF 的电容到地即         |

|          |   |                               | 可。                                            |

|          |   |                               | ADC 参考电压                                      |

| ADC_VREF | Α | 98                            | ADC 的输入参考电压,可以选择内部产生,或是由外部输入。此管脚              |

|          |   |                               | 必须接一 1~10uF 电容到地(GND)以提升 ADC 转换的稳定度。          |

|          |   | 6,<br>45,<br>113              | I/O 的 VDD 电源信号                                |

| VDD      | Р |                               | VDD 为 3.3V 输入。                                |

|          |   |                               | LDO VDD                                       |

| LDO_VDD  | Р | 1,<br>72,                     | 内部 LDO(Low Dropout Regulator)的电源(3.3V)输入,用以产生 |

|          |   |                               | 1.8V 电源输出。                                    |

| 100 000  | 7 | 71,                           | LDO GND                                       |

| LDO_GND  | Р | 128                           | LDO 的接地线。                                     |

| L DO OUT |   | 73                            | LDO 电压输出                                      |

| LDO_OUT  | Р |                               | LDO 1.8V 电源输出,于靠近输出端处接一电容到地以提升滤波效果。           |

| 100.040  | ) | 4                             | LDO 的滤波电容接点                                   |

| LDO_CAP  | Р |                               | 必须接一 1uF 以上的滤波电容到地以减少杂讯干扰。                    |

|          |   | 43,<br>112                    | 内核电路的 VDD 电源                                  |

| CORE_VDD | Р |                               | 内部核心电路的 VDD 电源为 1.8V,请接到 LDO_OUT,并于靠近输入       |

|          |   |                               | 端处接一 1uF 以上的滤波电容到地以减少杂讯干扰。                    |

|          | Р | 95,                           | ADC VDD                                       |

| ADC_VDD  |   | 96                            | 内部 ADC 电源(3.3V)输入。请将此信号接至 3.3V。               |

|          | _ | 97                            | ADC GND                                       |

| ADC_GND  | Р |                               | 内部 ADC 的接地线。请将此信号接地。                          |

| DAG 1/DD | _ | 66                            | DAC VDD                                       |

| DAC_VDD  | Р |                               | 内部 DAC 电源(3.3V)输入。请将此信号接至 3.3V。               |

| DAC_GND  | _ | 70                            | DAC GND                                       |

|          | Р |                               | 内部 DAC 的接地线。请将此信号接地。                          |

| GND      |   | 5,<br>9,<br>44,<br>94,<br>111 |                                               |

|          | P |                               | GND                                           |

|          |   |                               | 内核电路及 IO 的接地线。                                |

|          |   |                               |                                               |

## 5. 产品封装