# LPC2212/LPC2214

16/32-bit ARM microcontrollers; 128/256 kB ISP/IAP Flash with 10-bit ADC and external memory interface

Rev. 02 — 23 December 2004

Product data

## 1. General description

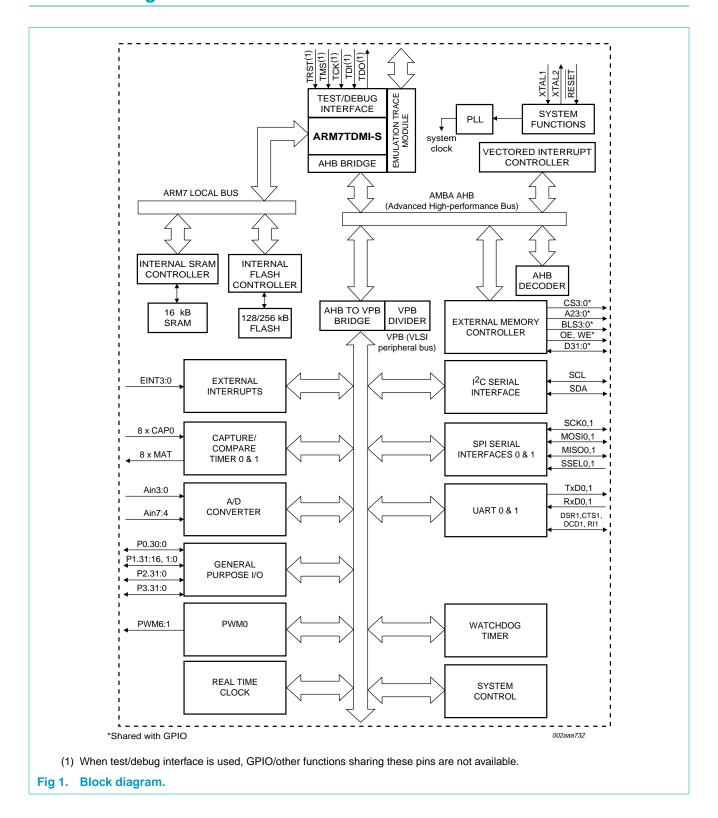

The LPC2212/LPC2214 are based on a 16/32 bit ARM7TDMI-S™ CPU with real-time emulation and embedded trace support, together with 128/256 kilobytes (kB) of embedded high speed flash memory. A 128-bit wide memory interface and a unique accelerator architecture enable 32-bit code execution at maximum clock rate. For critical code size applications, the alternative 16-bit Thumb® Mode reduces code by more than 30 % with minimal performance penalty.

With their 144 pin package, low power consumption, various 32-bit timers, 8-channel 10-bit ADC, PWM channels and up to 9 external interrupt pins these microcontrollers are particularly suitable for industrial control, medical systems, access control and point-of-sale. Number of available GPIOs ranges from 76 (with external memory) through 112 pins (single-chip). With a wide range of serial communications interfaces, they are also very well suited for communication gateways, protocol converters and embedded soft modems as well as many other general-purpose applications.

### 2. Features

### 2.1 Key features

- 16/32-bit ARM7TDMI-S microcontroller in a LQFP144 package.

- 16 kB on-chip Static RAM and 128/256 kB on-chip Flash Program Memory. 128-bit wide interface/accelerator enables high speed 60 MHz operation.

- In-System Programming (ISP) and In-Application Programming (IAP) via on-chip boot-loader software. Flash programming takes 1 ms per 512 byte line. Single sector or full chip erase takes 400 ms.

- EmbeddedICE-RT and Embedded Trace interfaces offer real-time debugging with the on-chip RealMonitor<sup>™</sup> software as well as high speed real-time tracing of instruction execution.

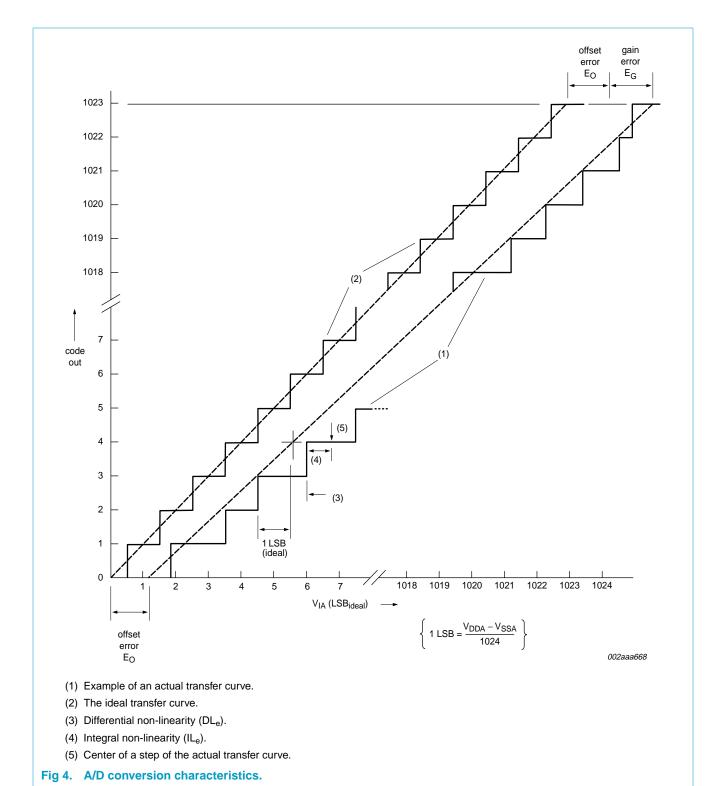

- **Eight** channel 10-bit A/D converter with conversion time as low as 2.44 μs.

- Two 32-bit timers (with 4 capture and 4 compare channels), PWM unit (6 outputs), Real Time Clock and Watchdog.

- Multiple serial interfaces including two UARTs (16C550), Fast I<sup>2</sup>C (400 kbits/s) and two SPIs.

- Vectored Interrupt Controller with configurable priorities and vector addresses.

- Configurable external memory interface with up to four banks, each up to 16 Mb and 8/16/32 bit data width.

- Up to 112 general purpose I/O pins (5 V tolerant). Up to 9 edge or level sensitive external interrupt pins available.

- 60 MHz maximum CPU clock available from programmable on-chip Phase-Locked Loop with settling time of 100 µs.

- On-chip crystal oscillator with an operating range of 1 MHz to 30 MHz.

- Two low power modes, Idle and Power-down.

- Processor wake-up from Power-down mode via external interrupt.

- Individual enable/disable of peripheral functions for power optimization.

- Dual power supply:

- CPU operating voltage range of 1.65 V to 1.95 V (1.8 V  $\pm$  0.15 V).

- ◆ I/O power supply range of 3.0 V to 3.6 V (3.3 V ± 10 %) with 5 V tolerant I/O pads. 16/32-bit ARM7TDMI-S processor.

# 3. Ordering information

**Table 1: Ordering information**

| Type number   | Package |                                                                                     |          |  |

|---------------|---------|-------------------------------------------------------------------------------------|----------|--|

|               | Name    | Description                                                                         | Version  |  |

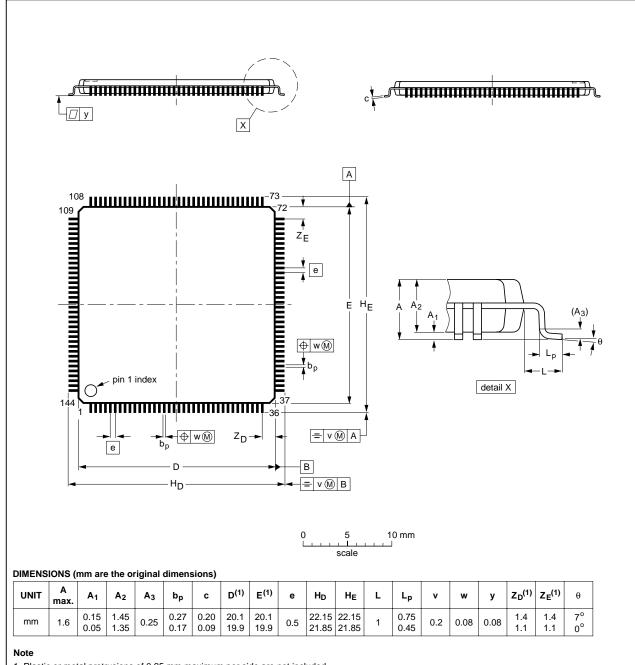

| LPC2212FBD144 | LQFP144 | plastic low-profile quad flat package; 144 leads; body 20 × 20 × 1.4 mm             | SOT486-1 |  |

| LPC2214FBD144 | LQFP144 | plastic low-profile quad flat package; 144 leads; body $20 \times 20 \times 1.4$ mm | SOT486-1 |  |

### 3.1 Ordering options

Table 2: Part options

| Type number   | Flash memory | RAM   | CAN | Temperature range (°C) |

|---------------|--------------|-------|-----|------------------------|

| LPC2212FBD144 | 128 kB       | 16 kB | -   | -40 to +85             |

| LPC2214FBD144 | 256 kB       | 16 kB | -   | -40 to +85             |

# 4. Block diagram

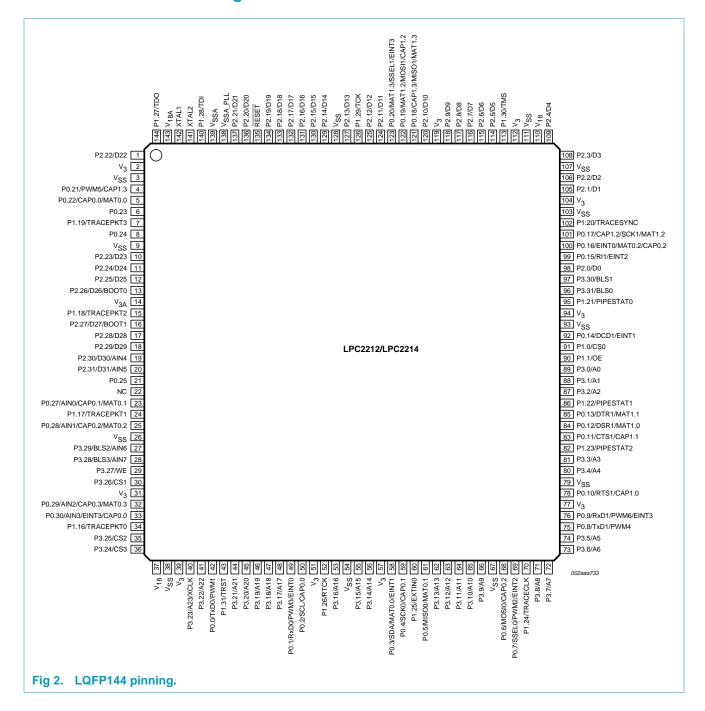

# 5. Pinning information

### 5.1 Pinning

# 5.2 Pin description

Table 3: Pin description

| Symbol      | Pin  | Type | Description                                                                                                                                                                                               |

|-------------|------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P0.0 to P0. | 31   | I/O  | <b>Port 0:</b> Port 0 is a 32-bit bi-directional I/O port with individual direction controls for each bit. The operation of port 0 pins depends upon the pin function selected via the Pin Connect Block. |

|             |      |      | Pins 26 and 31 of port 0 are not available.                                                                                                                                                               |

| P0.0        | 42 O | 0    | TxD0 — Transmitter output for UART0.                                                                                                                                                                      |

|             |      | 0    | <b>PWM1</b> — Pulse Width Modulator output 1.                                                                                                                                                             |

| P0.1        | 49   | I    | RxD0 — Receiver input for UART0.                                                                                                                                                                          |

|             |      | 0    | <b>PWM3</b> — Pulse Width Modulator output 3.                                                                                                                                                             |

|             |      | I    | EINT0 — External interrupt 0 input                                                                                                                                                                        |

| P0.2        | 50   | I/O  | <b>SCL</b> — I <sup>2</sup> C clock input/output. Open drain output (for I <sup>2</sup> C compliance).                                                                                                    |

|             |      | I    | CAP0.0 — Capture input for Timer0, channel 0.                                                                                                                                                             |

| P0.3        | 58   | I/O  | <b>SDA</b> — I <sup>2</sup> C data input/output. Open drain output (for I <sup>2</sup> C compliance).                                                                                                     |

|             |      | 0    | MAT0.0 — Match output for Timer0, channel 0.                                                                                                                                                              |

|             |      | I    | EINT1 — External interrupt 1 input.                                                                                                                                                                       |

| P0.4        | 59   | I/O  | <b>SCK0</b> — Serial clock for SPI0. SPI <sup>™</sup> clock output from master or input to slave.                                                                                                         |

|             |      | 1    | CAP0.1 — Capture input for Timer0, channel 1.                                                                                                                                                             |

| P0.5        | 61   | I/O  | MISO0 — Master In Slave OUT for SPI0. Data input to SPI master or data<br>output from SPI slave.                                                                                                          |

|             |      | 0    | MAT0.1 — Match output for Timer0, channel 1.                                                                                                                                                              |

| P0.6        | 68   | I/O  | <b>MOSI0</b> — Master Out Slave In for SPI0. Data output from SPI master or data input to SPI slave.                                                                                                      |

|             |      | I    | CAP0.2 — Capture input for Timer0, channel 2.                                                                                                                                                             |

| P0.7        | 69   | I    | SSEL0 — Slave Select for SPI0. Selects the SPI interface as a slave.                                                                                                                                      |

|             |      | Ο    | <b>PWM2</b> — Pulse Width Modulator output 2.                                                                                                                                                             |

|             |      | 1    | EINT2 — External interrupt 2 input.                                                                                                                                                                       |

| P0.8        | 75   | 0    | TxD1 — Transmitter output for UART1.                                                                                                                                                                      |

|             |      | 0    | <b>PWM4</b> — Pulse Width Modulator output 4.                                                                                                                                                             |

| P0.9        | 76   | I    | RxD1 — Receiver input for UART1.                                                                                                                                                                          |

|             |      | 0    | <b>PWM6</b> — Pulse Width Modulator output 6.                                                                                                                                                             |

|             |      | I    | EINT3 — External interrupt 3 input.                                                                                                                                                                       |

| P0.10       | 78   | 0    | RTS1 — Request to Send output for UART1.                                                                                                                                                                  |

|             |      | I    | CAP1.0 — Capture input for Timer1, channel 0.                                                                                                                                                             |

| P0.11       | 83   | I    | CTS1 — Clear to Send input for UART1.                                                                                                                                                                     |

|             |      | I    | CAP1.1 — Capture input for Timer1, channel 1.                                                                                                                                                             |

| P0.12       | 84   |      | DSR1 — Data Set Ready input for UART1.                                                                                                                                                                    |

Table 3:

Pin description...continued

| Symbol   | Pin | Type | Description                                                                                                                           |

|----------|-----|------|---------------------------------------------------------------------------------------------------------------------------------------|

|          |     | 0    | MAT1.0 — Match output for Timer1, channel 0.                                                                                          |

| P0.13    | 85  | 0    | DTR1 — Data Terminal Ready output for UART1.                                                                                          |

|          |     | 0    | MAT1.1 — Match output for Timer1, channel 1.                                                                                          |

| P0.14 92 |     | I    | DCD1 — Data Carrier Detect input for UART1.                                                                                           |

|          |     | I    | EINT1 — External interrupt 1 input.                                                                                                   |

|          |     |      | Note: LOW on this pin while $\overline{\text{RESET}}$ is LOW forces on-chip boot-loader to take over control of the part after reset. |

| P0.15    | 99  | I    | RI1 — Ring Indicator input for UART1.                                                                                                 |

|          |     | I    | EINT2 — External interrupt 2 input.                                                                                                   |

| P0.16    | 100 | I    | EINT0 — External interrupt 0 input.                                                                                                   |

|          |     | 0    | <b>MAT0.2</b> — Match output for Timer0, channel 2.                                                                                   |

|          |     | I    | CAP0.2 — Capture input for Timer0, channel 2.                                                                                         |

| P0.17    | 101 | I    | CAP1.2 — Capture input for Timer1, channel 2.                                                                                         |

|          |     | I/O  | SCK1 — Serial Clock for SPI1. SPI clock output from master or input to slave.                                                         |

|          |     | 0    | MAT1.2 — Match output for Timer1, channel 2.                                                                                          |

| P0.18    | 121 | I    | CAP1.3 — Capture input for Timer1, channel 3.                                                                                         |

|          |     | I/O  | <b>MISO1</b> — Master In Slave Out for SPI1. Data input to SPI master or data output from SPI slave.                                  |

|          |     | 0    | MAT1.3 — Match output for Timer1, channel 3.                                                                                          |

| P0.19    | 122 | 0    | MAT1.2 — Match output for Timer1, channel 2.                                                                                          |

|          |     | I/O  | <b>MOSI1</b> — Master Out Slave In for SPI1. Data output from SPI master or data input to SPI slave.                                  |

|          |     | I    | CAP1.2 — Capture input for Timer1, channel 2.                                                                                         |

| P0.20    | 123 | 0    | MAT1.3 — Match output for Timer1, channel 3.                                                                                          |

|          |     | I    | SSEL1 — Slave Select for SPI1. Selects the SPI interface as a slave.                                                                  |

|          |     | I    | EINT3 — External interrupt 3 input.                                                                                                   |

| P0.21    | 4   | 0    | PWM5 — Pulse Width Modulator output 5.                                                                                                |

|          |     | I    | CAP1.3 — Capture input for TIMER1, channel 3.                                                                                         |

| P0.22    | 5   | I    | CAP0.0 — Capture input for Timer0, channel 0.                                                                                         |

|          |     | 0    | MAT0.0 — Match output for Timer0, channel 0.                                                                                          |

| P0.23    | 6   | I/O  | General purpose bidirectional digital port only.                                                                                      |

| P0.24    | 8   | I/O  | General purpose bidirectional digital port only.                                                                                      |

| P0.25    | 21  | I/O  | General purpose bidirectional digital port only.                                                                                      |

| P0.27    | 23  | l    | <b>AIN0</b> — A/D converter, input 0. This analog input is always connected to its pin.                                               |

|          |     | I    | CAP0.1 — Capture input for Timer0, channel 1.                                                                                         |

|          |     | 0    | MAT0.1 — Match output for Timer0, channel 1.                                                                                          |

Table 3: Pin description...continued

| Table 3:               | Pin description. | continued |                                                                                                                                                                                                           |  |  |

|------------------------|------------------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Symbol                 | Pin              | Туре      | Description                                                                                                                                                                                               |  |  |

| P0.28                  | 25               | I         | <b>AIN1</b> — A/D converter, input 1. This analog input is always connected to its pin.                                                                                                                   |  |  |

|                        |                  | I         | CAP0.2 — Capture input for Timer0, channel 2.                                                                                                                                                             |  |  |

|                        |                  | 0         | MAT0.2 — Match output for Timer0, channel 2.                                                                                                                                                              |  |  |

| P0.29                  | 32               | I         | <b>AIN2</b> — A/D converter, input 2. This analog input is always connected to its pin.                                                                                                                   |  |  |

|                        |                  | I         | CAP0.3 — Capture input for Timer0, Channel 3.                                                                                                                                                             |  |  |

|                        |                  | 0         | MAT0.3 — Match output for Timer0, channel 3.                                                                                                                                                              |  |  |

| P0.30                  | 33               | I         | <b>AIN3</b> — A/D converter, input 3. This analog input is always connected to its pin.                                                                                                                   |  |  |

|                        |                  | I         | EINT3 — External interrupt 3 input.                                                                                                                                                                       |  |  |

|                        |                  | I         | CAP0.0 — Capture input for Timer0, channel 0.                                                                                                                                                             |  |  |

| P1.0 to P <sup>2</sup> | 1.31             | I/O       | <b>Port 1:</b> Port 1 is a 32-bit bi-directional I/O port with individual direction controls for each bit. The operation of port 1 pins depends upon the pin function selected via the Pin Connect Block. |  |  |

|                        |                  |           | Pins 0 through 15 of port 1 are not available.                                                                                                                                                            |  |  |

| P1.0                   | 91               | 0         | CS0 — Low-active Chip Select 0 signal.                                                                                                                                                                    |  |  |

|                        |                  |           | (Bank 0 addresses range 8000 0000 - 80FF FFFF)                                                                                                                                                            |  |  |

| P1.1                   | 90               | 0         | OE — Low-active Output Enable signal.                                                                                                                                                                     |  |  |

| P1.16                  | 34               | 0         | TRACEPKT0 — Trace Packet, bit 0. Standard I/O port with internal pull-up.                                                                                                                                 |  |  |

| P1.17                  | 24               | 0         | TRACEPKT1 — Trace Packet, bit 1. Standard I/O port with internal pull-up.                                                                                                                                 |  |  |

| P1.18                  | 15               | 0         | TRACEPKT2 — Trace Packet, bit 2. Standard I/O port with internal pull-u                                                                                                                                   |  |  |

| P1.19                  | 7                | 0         | TRACEPKT3 — Trace Packet, bit 3. Standard I/O port with internal pu                                                                                                                                       |  |  |

| P1.20                  | 102              | 0         | TRACESYNC — Trace Synchronization. Standard I/O port with internal pull-up.  Note: LOW on this pin while RESET is LOW, enables pins P1.25:16 to                                                           |  |  |

|                        |                  |           | operate as Trace port after reset.                                                                                                                                                                        |  |  |

| P1.21                  | 95               | 0         | PIPESTAT0 — Pipeline Status, bit 0. Standard I/O port with internal pull-up.                                                                                                                              |  |  |

| P1.22                  | 86               | 0         | PIPESTAT1 — Pipeline Status, bit 1. Standard I/O port with internal pull-up.                                                                                                                              |  |  |

| P1.23                  | 82               | 0         | PIPESTAT2 — Pipeline Status, bit 2. Standard I/O port with internal pull-up.                                                                                                                              |  |  |

| P1.24                  | 70               | 0         | TRACECLK — Trace Clock. Standard I/O port with internal pull-up.                                                                                                                                          |  |  |

| P1.25                  | 60               | I         | EXTINO — External Trigger Input. Standard I/O with internal pull-up.                                                                                                                                      |  |  |

| P1.26                  | 52               | I/O       | <b>RTCK</b> — Returned Test Clock output. Extra signal added to the JTAG port. Assists debugger synchronization when processor frequency varies. Bi-directional pin with internal pull-up.                |  |  |

|                        |                  |           | Note: LOW on this pin while $\overline{\text{RESET}}$ is LOW, enables pins P1.31:26 to operate as Debug port after reset.                                                                                 |  |  |

| P1.27                  | 144              | 0         | TDO — Test Data out for JTAG interface.                                                                                                                                                                   |  |  |

| P1.28                  | 140              | I         | TDI — Test Data in for JTAG interface.                                                                                                                                                                    |  |  |

| P1.29                  | 126              | I         | TCK — Test Clock for JTAG interface.                                                                                                                                                                      |  |  |

| P1.30                  | 113              | I         | TMS — Test Mode Select for JTAG interface.                                                                                                                                                                |  |  |

| P1.31                  | 43               | I         | TRST — Test Reset for JTAG interface.                                                                                                                                                                     |  |  |

Table 3: Pin description...continued

| Table 3:   | Pin description. | continued |                                                                                                                                                                                                            |

|------------|------------------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Symbol     | Pin              | Туре      | Description                                                                                                                                                                                                |

| P2.0 to P2 | 2.31             | I/O       | <b>Port 2</b> — Port 2 is a 32-bit bi-directional I/O port with individual direction controls for each bit. The operation of port 2 pins depends upon the pin function selected via the Pin Connect Block. |

| P2.0       | 98               | I/O       | <b>D0</b> — External memory data line 0.                                                                                                                                                                   |

| P2.1       | 105              | I/O       | D1 — External memory data line 1.                                                                                                                                                                          |

| 2.2        | 106              | I/O       | D2 — External memory data line 2.                                                                                                                                                                          |

| P2.3       | 108              | I/O       | D3 — External memory data line 3.                                                                                                                                                                          |

| 2.4        | 109              | I/O       | <b>D4</b> — External memory data line 4.                                                                                                                                                                   |

| P2.5       | 114              | I/O       | <b>D5</b> — External memory data line 5.                                                                                                                                                                   |

| P2.6       | 115              | I/O       | <b>D6</b> — External memory data line 6.                                                                                                                                                                   |

| P2.7       | 116              | I/O       | <b>D7</b> — External memory data line 7.                                                                                                                                                                   |

| P2.8       | 117              | I/O       | <b>D8</b> — External memory data line 8.                                                                                                                                                                   |

| P2.9       | 118              | I/O       | <b>D9</b> — External memory data line 9.                                                                                                                                                                   |

| P2.10      | 120              | I/O       | D10 — External memory data line 10.                                                                                                                                                                        |

| P2.11      | 124              | I/O       | D11 — External memory data line 11.                                                                                                                                                                        |

| P2.12      | 125              | I/O       | D12 — External memory data line 12.                                                                                                                                                                        |

| P2.13      | 127              | I/O       | D13 — External memory data line 13.                                                                                                                                                                        |

| P2.14      | 129              | I/O       | D14 — External memory data line 14.                                                                                                                                                                        |

| P2.15      | 130              | I/O       | D15 — External memory data line 15.                                                                                                                                                                        |

| P2.16      | 131              | I/O       | D16 — External memory data line 16.                                                                                                                                                                        |

| P2.17      | 132              | I/O       | D17 — External memory data line 17.                                                                                                                                                                        |

| P2.18      | 133              | I/O       | D18 — External memory data line 18.                                                                                                                                                                        |

| P2.19      | 134              | I/O       | D19 — External memory data line 19.                                                                                                                                                                        |

| P2.20      | 136              | I/O       | <b>D20</b> — External memory data line 20.                                                                                                                                                                 |

| P2.21      | 137              | I/O       | D21 — External memory data line 21.                                                                                                                                                                        |

| P2.22      | 1                | I/O       | D22 — External memory data line 22.                                                                                                                                                                        |

| P2.23      | 10               | I/O       | D23 — External memory data line 23.                                                                                                                                                                        |

| P2.24      | 11               | I/O       | <b>D24</b> — External memory data line 24.                                                                                                                                                                 |

| P2.25      | 12               | I/O       | D25 — External memory data line 25.                                                                                                                                                                        |

| P2.26      | 13               | I/O       | <b>D26</b> — External memory data line 26.                                                                                                                                                                 |

|            |                  | I         | <b>BOOT0</b> — While RESET is low, together with BOOT1 controls booting and internal operation. Internal pull-up ensures high state if pin is left unconnected.                                            |

| 2.27       | 16               | I/O       | <b>D27</b> — External memory data line 27.                                                                                                                                                                 |

|            |                  | I         | <b>BOOT1</b> — While RESET is low, together with BOOT0 controls booting and internal operation. Internal pull-up ensures high state if pin is left unconnected.                                            |

|            |                  |           | BOOT1:0=00 selects 8-bit memory on CS0 for boot.                                                                                                                                                           |

|            |                  |           | BOOT1:0=01 selects 16-bit memory on CS0 for boot.                                                                                                                                                          |

|            |                  |           | BOOT1:0=10 selects 32-bit memory on CS0 for boot.                                                                                                                                                          |

|            |                  |           | BOOT1:0=11 selects Internal Flash memory.                                                                                                                                                                  |

| P2.28      | 17               | I/O       | D28 — External memory data line 28.                                                                                                                                                                        |

Table 3: Pin description...continued

| Table 3: P Symbol | in description |      | Description                                                                                                           |

|-------------------|----------------|------|-----------------------------------------------------------------------------------------------------------------------|

|                   | Pin            | Type | Description                                                                                                           |

| P2.29             | 18             | I/O  | D29 — External memory data line 29.                                                                                   |

| P2.30             | 19             | I/O  | D30 — External memory data line 30.                                                                                   |

|                   |                | I    | <b>AIN4</b> — A/D converter, input 4. This analog input is always connected to its pin.                               |

| P2.31             | 20             | I/O  | D31 — External memory data line 31.                                                                                   |

|                   |                | I    | <b>AIN5</b> — A/D converter, input 5. This analog input is always connected to its pin.                               |

| P3.0 to P3.31     | 1              | I/O  | Port 3 — Port 3 is a 32-bit bi-directional I/O port with individual direction                                         |

|                   |                |      | controls for each bit. The operation of port 3 pins depends upon the pin function selected via the Pin Connect Block. |

| P3.0              | 89             | 0    | A0 — External memory address line 0.                                                                                  |

| P3.1              | 88             | 0    | A1 — External memory address line 1.                                                                                  |

| P3.2              | 87             | 0    | A2 — External memory address line 2.                                                                                  |

| P3.3              | 81             | 0    | A3 — External memory address line 3.                                                                                  |

| P3.4              | 80             | 0    | A4 — External memory address line 4.                                                                                  |

| P3.5              | 74             | 0    | A5 — External memory address line 5.                                                                                  |

| P3.6              | 73             | 0    | A6 — External memory address line 6.                                                                                  |

| P3.7              | 72             | 0    | A7 — External memory address line 7.                                                                                  |

| P3.8              | 71             | 0    | A8 — External memory address line 8.                                                                                  |

| P3.9              | 66             | 0    | A9 — External memory address line 9.                                                                                  |

| P3.10             | 65             | 0    | A10 — External memory address line 10.                                                                                |

| P3.11             | 64             | 0    | A11 — External memory address line 11.                                                                                |

| P3.12             | 63             | 0    | A12 — External memory address line 12.                                                                                |

| P3.13             | 62             | 0    | A13 — External memory address line 13.                                                                                |

| P3.14             | 56             | 0    | A14 — External memory address line 14.                                                                                |

| P3.15             | 55             | 0    | A15 — External memory address line 15.                                                                                |

| P3.16             | 53             | 0    | A16 — External memory address line 16.                                                                                |

| P3.17             | 48             | 0    | A17 — External memory address line 17.                                                                                |

| P3.18             | 47             | 0    | A18 — External memory address line 18.                                                                                |

| P3.19             | 46             | 0    | A19 — External memory address line 19.                                                                                |

| P3.20             | 45             | 0    | A20 — External memory address line 20.                                                                                |

| P3.21             | 44             | 0    | A21 — External memory address line 21.                                                                                |

| P3.22             | 41             | 0    | A22 — External memory address line 22.                                                                                |

| P3.23             | 40             | 0    | A23 — External memory address line 23.                                                                                |

|                   |                | 0    | XCLK — Clock output.                                                                                                  |

| P3.24             | 36             | 0    | CS3 — Low-active Chip Select 3 signal.                                                                                |

|                   |                |      | (Bank 3 addresses range 8300 0000 - 83FF FFFF)                                                                        |

| P3.25             | 35             | 0    | CS2 — Low-active Chip Select 2signal.                                                                                 |

|                   |                |      | (Bank 2 addresses range 8200 0000 - 82FF FFFF)                                                                        |

| P3.26             | 30             | 0    | CS1 — Low-active Chip Select 1 signal.                                                                                |

|                   |                |      | (Bank 1 addresses range 8100 0000 - 81FF FFFF)                                                                        |

| P3.27             | 29             | 0    | WE — Low-active Write enable signal.                                                                                  |

Table 3:

Pin description...continued

| Symbol               | Pin                                                       | Туре | Description                                                                                                                                                                                                            |

|----------------------|-----------------------------------------------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P3.28                | 28                                                        | 0    | BLS3 — Low-active Byte Lane Select signal (Bank 3).                                                                                                                                                                    |

|                      |                                                           | 1    | <b>AIN7</b> — A/D converter, input 7. This analog input is always connected to its pin.                                                                                                                                |

| P3.29                | 27                                                        | 0    | BLS2 — Low-active Byte Lane Select signal (Bank 2).                                                                                                                                                                    |

|                      |                                                           | 1    | <b>AIN6</b> — A/D converter, input 6. This analog input is always connected to its pin.                                                                                                                                |

| P3.30                | 97                                                        | 0    | BLS1 — Low-active Byte Lane Select signal (Bank 1).                                                                                                                                                                    |

| P3.31                | 96                                                        | 0    | BLS0 — Low-active Byte Lane Select signal (Bank 0).                                                                                                                                                                    |

| NC                   | 22                                                        |      | Pin not connected.                                                                                                                                                                                                     |

| RESET                | 135                                                       | I    | <b>External Reset input:</b> A LOW on this pin resets the device, causing I/O ports and peripherals to take on their default states, and processor execution to begin at address 0. TTL with hysteresis, 5 V tolerant. |

| XTAL1                | 142                                                       | I    | Input to the oscillator circuit and internal clock generator circuits.                                                                                                                                                 |

| XTAL2                | 141                                                       | 0    | Output from the oscillator amplifier.                                                                                                                                                                                  |

| V <sub>SS</sub>      | 3, 9, 26, 38,<br>54, 67, 79,<br>93, 103, 107,<br>111, 128 | I    | Ground: 0 V reference.                                                                                                                                                                                                 |

| V <sub>SSA</sub>     | 139                                                       | I    | <b>Analog Ground:</b> 0 V reference. This should nominally be the same voltage as $V_{SS}$ , but should be isolated to minimize noise and error.                                                                       |

| V <sub>SSA_PLL</sub> | 138                                                       | 1    | <b>PLL Analog Ground:</b> 0 V reference. This should nominally be the same voltage as $V_{SS}$ , but should be isolated to minimize noise and error.                                                                   |

| V <sub>18</sub>      | 37, 110                                                   | I    | <b>1.8 V Core Power Supply:</b> This is the power supply voltage for internal circuitry.                                                                                                                               |

| V <sub>18A</sub>     | 143                                                       | I    | <b>Analog 1.8 V Core Power Supply:</b> This is the power supply voltage for internal circuitry. This should be nominally the same voltage as $V_{18}$ but should be isolated to minimize noise and error.              |

| V <sub>3</sub>       | 2, 31, 39, 51,<br>57, 77, 94,<br>104, 112, 119            | I    | <b>3.3 V Pad Power Supply:</b> This is the power supply voltage for the I/O ports.                                                                                                                                     |

| V <sub>3A</sub>      | 14                                                        | I    | Analog 3.3 V Pad Power Supply: This should be nominally the same voltage as $\rm V_3$ but should be isolated to minimize noise and error.                                                                              |

# 6. Functional description

Details of the LPC2212/LPC2214 systems and peripheral functions are described in the following sections.

#### 6.1 Architectural overview

The ARM7TDMI-S is a general purpose 32-bit microprocessor, which offers high performance and very low power consumption. The ARM® architecture is based on Reduced Instruction Set Computer (RISC) principles, and the instruction set and related decode mechanism are much simpler than those of microprogrammed Complex Instruction Set Computers. This simplicity results in a high instruction throughput and impressive real-time interrupt response from a small and cost-effective processor core.

Pipeline techniques are employed so that all parts of the processing and memory systems can operate continuously. Typically, while one instruction is being executed, its successor is being decoded, and a third instruction is being fetched from memory.

The ARM7TDMI-S processor also employs a unique architectural strategy known as Thumb, which makes it ideally suited to high-volume applications with memory restrictions, or applications where code density is an issue.

The key idea behind Thumb is that of a super-reduced instruction set. Essentially, the ARM7TDMI-S processor has two instruction sets:

- The standard 32-bit ARM set.

- A 16-bit Thumb set.

The Thumb set's 16-bit instruction length allows it to approach twice the density of standard ARM code while retaining most of the ARM's performance advantage over a traditional 16-bit processor using 16-bit registers. This is possible because Thumb code operates on the same 32-bit register set as ARM code.

Thumb code is able to provide up to 65 % of the code size of ARM, and 160 % of the performance of an equivalent ARM processor connected to a 16-bit memory system.

### 6.2 On-Chip Flash program memory

The LPC2212/LPC2214 incorporate a 128 kB and 256 kB Flash memory system respectively. This memory may be used for both code and data storage. Programming of the Flash memory may be accomplished in several ways. It may be programmed In System via the serial port. The application program may also erase and/or program the Flash while the application is running, allowing a great degree of flexibility for data storage field firmware upgrades, etc. When on-chip bootloader is used, 120/248 kB of Flash memory is available for user code.

The LPC2212/LPC2214 Flash memory provides a minimum of 100,000 erase/write cycles and 20 years of data retention.

On-chip bootloader (as of revision 1.60) provides Code Read Protection (CRP) for the LPC2212/LPC2214 on-chip Flash memory. When the CRP is enabled, the JTAG debug port, external memory boot and ISP commands accessing either the on-chip

RAM or Flash memory are disabled. However, the ISP Flash Erase command can be executed at any time (no matter whether the CRP is on or off). Removal of CRP is achieved by erasure of full on-chip user Flash. With the CRP off, full access to the chip via the JTAG and/or ISP is restored.

### 6.3 On-Chip static RAM

On-Chip static RAM may be used for code and/or data storage. The SRAM may be accessed as 8-bits, 16-bits, and 32-bits. The LPC2212/LPC2214 provide 16 kB of static RAM.

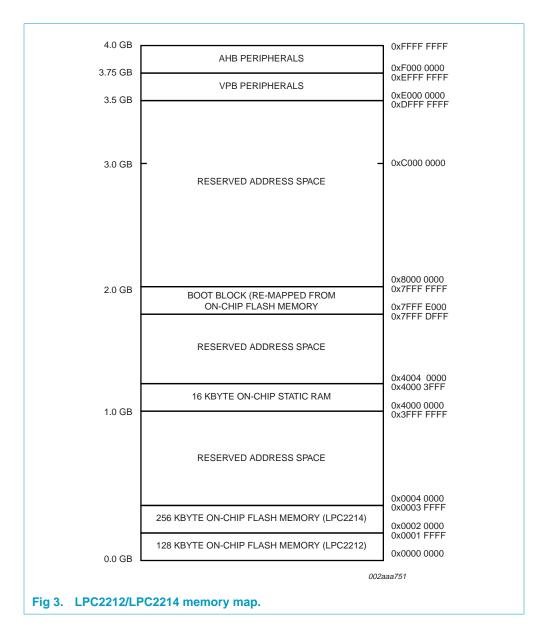

### 6.4 Memory map

The LPC2212/LPC2214 memory maps incorporate several distinct regions, as shown in the following figures.

In addition, the CPU interrupt vectors may be re-mapped to allow them to reside in either Flash memory (the default) or on-chip static RAM. This is described in Section 6.20 "System control".

### 6.5 Interrupt controller

The Vectored Interrupt Controller (VIC) accepts all of the interrupt request inputs and categorizes them as FIQ, vectored IRQ, and non-vectored IRQ as defined by programmable settings. The programmable assignment scheme means that priorities of interrupts from the various peripherals can be dynamically assigned and adjusted.

Fast Interrupt reQuest (FIQ) has the highest priority. If more than one request is assigned to FIQ, the VIC combines the requests to produce the FIQ signal to the ARM processor. The fastest possible FIQ latency is achieved when only one request is classified as FIQ, because then the FIQ service routine can simply start dealing with that device. But if more than one request is assigned to the FIQ class, the FIQ service routine can read a word from the VIC that identifies which FIQ source(s) is (are) requesting an interrupt.

Vectored IRQs have the middle priority. Sixteen of the interrupt requests can be assigned to this category. Any of the interrupt requests can be assigned to any of the 16 vectored IRQ slots, among which slot 0 has the highest priority and slot 15 has the lowest.

Non-vectored IRQs have the lowest priority.

The VIC combines the requests from all the vectored and non-vectored IRQs to produce the IRQ signal to the ARM processor. The IRQ service routine can start by reading a register from the VIC and jumping there. If any of the vectored IRQs are requesting, the VIC provides the address of the highest-priority requesting IRQs service routine, otherwise it provides the address of a default routine that is shared by all the non-vectored IRQs. The default routine can read another VIC register to see what IRQs are active.

#### 6.5.1 Interrupt sources

Table 4 lists the interrupt sources for each peripheral function. Each peripheral device has one interrupt line connected to the Vectored Interrupt Controller, but may have several interrupt flags. Individual interrupt flags may also represent more than one interrupt source.

Table 4: Interrupt sources

| Block            | Flag(s)                                         | VIC channel # |

|------------------|-------------------------------------------------|---------------|

| WDT              | Watchdog Interrupt (WDINT)                      | 0             |

| -                | Reserved for software interrupts only           | 1             |

| ARM Core         | Embedded ICE, DbgCommRx                         | 2             |

| ARM Core         | Embedded ICE, DbgCommTx                         | 3             |

| Timer0           | Match 0 - 3 (MR0, MR1, MR2, MR3)                | 4             |

| Timer1           | Match 0 - 3 (MR0, MR1, MR2, MR3)                | 5             |

| UART0            | Rx Line Status (RLS)                            | 6             |

|                  | Transmit Holding Register empty (THRE)          |               |

|                  | Rx Data Available (RDA)                         |               |

|                  | Character Time-out Indicator (CTI)              |               |

| UART1            | Rx Line Status (RLS)                            | 7             |

|                  | Transmit Holding Register empty (THRE)          |               |

|                  | Rx Data Available (RDA)                         |               |

|                  | Character Time-out Indicator (CTI)              |               |

|                  | Modem Status Interrupt (MSI)                    |               |

| PWM0             | Match 0 - 6 (MR0, MR1, MR2, MR3, MR4, MR5, MR6) | 8             |

| I <sup>2</sup> C | SI (state change)                               | 9             |

| SPI0             | SPIF, MODF                                      | 10            |

| SPI1             | SPIF, MODF                                      | 11            |

| PLL              | PLL Lock (PLOCK)                                | 12            |

| RTC              | RTCCIF (Counter Increment), RTCALF (Alarm)      | 13            |

Table 4: Interrupt sources...continued

| Block          | Flag(s)                      | VIC channel # |

|----------------|------------------------------|---------------|

| System Control | External Interrupt 0 (EINT0) | 14            |

|                | External Interrupt 1 (EINT1) | 15            |

|                | External Interrupt 2 (EINT2) | 16            |

|                | External Interrupt 3 (EINT3) | 17            |

| A/D            | A/D Converter                | 18            |

#### 6.6 Pin connect block

The pin connect block allows selected pins of the microcontroller to have more than one function. Configuration registers control the multiplexers to allow connection between the pin and the on chip peripherals. Peripherals should be connected to the appropriate pins prior to being activated, and prior to any related interrupt(s) being enabled. Activity of any enabled peripheral function that is not mapped to a related pin should be considered undefined.

The Pin Control Module contains three registers as shown in Table 5.

Table 5:

| Address    | Name    | Description                    | Access     |

|------------|---------|--------------------------------|------------|

| 0xE002C000 | PINSEL0 | Pin function select register 0 | Read/Write |

| 0xE002C004 | PINSEL1 | Pin function select register 1 | Read/Write |

| 0xE002C014 | PINSEL2 | Pin function select register 2 | Read/Write |

### 6.7 Pin function select register 0 (PINSEL0 - 0xE002C000)

The PINSEL0 register controls the functions of the pins as per the settings listed in Table 6. The direction control bit in the IODIR register is effective only when the GPIO function is selected for a pin. For other functions, direction is controlled automatically. Settings other than those shown in Table 6 are reserved, and should not be used

Table 6: Pin function select register 0 (PINSEL0 - 0xE002C000)

| PINSEL0 | Pin name | Value |   | Function               | Value after Reset |

|---------|----------|-------|---|------------------------|-------------------|

| 1:0     | P0.0     | 0     | 0 | GPIO Port 0.0          | 0                 |

|         |          | 0     | 1 | TxD (UART0)            |                   |

|         |          | 1     | 0 | PWM1                   |                   |

|         |          | 1     | 1 | Reserved               |                   |

| 3:2     | P0.1     | 0     | 0 | GPIO Port 0.1          | 0                 |

|         |          | 0     | 1 | RxD (UART0)            |                   |

|         |          | 1     | 0 | PWM3                   |                   |

|         |          | 1     | 1 | EINT0                  |                   |

| 5:4     | P0.2     | 0     | 0 | GPIO Port 0.2          | 0                 |

|         |          | 0     | 1 | SCL (I <sup>2</sup> C) |                   |

|         |          | 1     | 0 | Capture 0.0 (Timer0)   |                   |

|         |          | 1     | 1 | Reserved               |                   |

Table 6: Pin function select register 0 (PINSEL0 - 0xE002C000)...continued

| Table 0. |          |       | gister ( | (FINSELU - 0XE002C000) |                   |

|----------|----------|-------|----------|------------------------|-------------------|

| PINSEL0  | Pin name | Value |          | Function               | Value after Reset |

| 7:6      | P0.3     | 0     | 0        | GPIO Port 0.3          | 0                 |

|          |          | 0     | 1        | SDA (I <sup>2</sup> C) | _                 |

|          |          | 1     | 0        | Match 0.0 (Timer0)     | _                 |

|          |          | 1     | 1        | EINT1                  |                   |

| 9:8      | P0.4     | 0     | 0        | GPIO Port 0.4          | 0                 |

|          |          | 0     | 1        | SCK (SPI0)             |                   |

|          |          | 1     | 0        | Capture 0.1 (Timer0)   |                   |

|          |          | 1     | 1        | Reserved               |                   |

| 11:10    | P0.5     | 0     | 0        | GPIO Port 0.5          | 0                 |

|          |          | 0     | 1        | MISO (SPI0)            |                   |

|          |          | 1     | 0        | Match 0.1 (Timer0)     |                   |

|          |          | 1     | 1        | Reserved               |                   |

| 13:12    | P0.6     | 0     | 0        | GPIO Port 0.6          | 0                 |

|          |          | 0     | 1        | MOSI (SPI0)            |                   |

|          |          | 1     | 0        | Capture 0.2 (Timer0)   |                   |

|          |          | 1     | 1        | Reserved               |                   |

| 15:14    | P0.7     | 0     | 0        | GPIO Port 0.7          | 0                 |

|          |          | 0     | 1        | SSEL (SPI0)            |                   |

|          |          | 1     | 0        | PWM2                   |                   |

|          |          | 1     | 1        | EINT2                  |                   |

| 17:16    | P0.8     | 0     | 0        | GPIO Port 0.8          | 0                 |

|          |          | 0     | 1        | TxD UART1              |                   |

|          |          | 1     | 0        | PWM4                   |                   |

|          |          | 1     | 1        | Reserved               |                   |

| 19:18    | P0.9     | 0     | 0        | GPIO Port 0.9          | 0                 |

|          |          | 0     | 1        | RxD (UART1)            |                   |

|          |          | 1     | 0        | PWM6                   |                   |

|          |          | 1     | 1        | EINT3                  |                   |

| 21:20    | P0.10    | 0     | 0        | GPIO Port 0.10         | 0                 |

|          |          | 0     | 1        | RTS (UART1)            | _                 |

|          |          | 1     | 0        | Capture 1.0 (Timer1)   | _                 |

|          |          | 1     | 1        | Reserved               |                   |

| 23:22    | P0.11    | 0     | 0        | GPIO Port 0.11         | 0                 |

|          |          | 0     | 1        | CTS (UART1)            |                   |

|          |          | 1     | 0        | Capture 1.1 (Timer1)   |                   |

|          |          | 1     | 1        | Reserved               |                   |

| 25:24    | P0.12    | 0     | 0        | GPIO Port 0.12         | 0                 |

|          |          | 0     | 1        | DSR (UART1)            |                   |

|          |          | 1     | 0        | Match 1.0 (Timer1)     | _                 |

|          |          | 1     | 1        | Reserved               |                   |

Table 6: Pin function select register 0 (PINSEL0 - 0xE002C000)...continued

| PINSEL0 | Pin name | Value |   | Function           | Value after Reset |

|---------|----------|-------|---|--------------------|-------------------|

| 27:26   | P0.13    | 0     | 0 | GPIO Port 0.13     | 0                 |

|         |          | 0     | 1 | DTR (UART1)        |                   |

|         |          | 1     | 0 | Match 1.1 (Timer1) |                   |

|         |          | 1     | 1 | Reserved           | -                 |

| 29:28   | P0.14    | 0     | 0 | GPIO Port 0.14     | 0                 |

|         |          | 0     | 1 | DCD (UART1)        |                   |

|         |          | 1     | 0 | EINT1              |                   |

|         |          | 1     | 1 | Reserved           |                   |

| 31:30   | P0.15    | 0     | 0 | GPIO Port 0.15     | 0                 |

|         |          | 0     | 1 | RI (UART1)         |                   |

|         |          | 1     | 0 | EINT2              |                   |

|         |          | 1     | 1 | Reserved           |                   |

### 6.8 Pin function select register 1 (PINSEL1 - 0xE002C004)

The PINSEL1 register controls the functions of the pins as per the settings listed in Table 7. The direction control bit in the IODIR register is effective only when the GPIO function is selected for a pin. For other functions direction is controlled automatically. Settings other than those shown in the table are reserved, and should not be used.

Table 7: Pin function select register 1 (PINSEL1 - 0xE002C004)

| PINSEL1 | Pin Name | Value |   | Function             | Value after<br>Reset |

|---------|----------|-------|---|----------------------|----------------------|

| 1:0     | P0.16    | 0     | 0 | GPIO Port 0.16       | 0                    |

|         |          | 0     | 1 | EINT0                |                      |

|         |          | 1     | 0 | Match 0.2 (Timer0)   |                      |

|         |          | 1     | 1 | Capture 0.2 (Timer0) |                      |

| 3:2     | P0.17    | 0     | 0 | GPIO Port 0.17       | 0                    |

|         |          | 0     | 1 | Capture 1.2 (Timer1) |                      |

|         |          | 1     | 0 | SCK (SPI1)           |                      |

|         |          | 1     | 1 | Match 1.2 (Timer1)   |                      |

| 5:4     | P0.18    | 0     | 0 | GPIO Port 0.18       | 0                    |

|         |          | 0     | 1 | Capture 1.3 (Timer1) |                      |

|         |          | 1     | 0 | MISO (SPI1)          |                      |

|         |          | 1     | 1 | Match 1.3 (Timer1)   |                      |

| 7:6     | P0.19    | 0     | 0 | GPIO Port 0.19       | 0                    |

|         |          | 0     | 1 | Match 1.2 (Timer1)   |                      |

|         |          | 1     | 0 | MOSI (SPI1)          |                      |

|         |          | 1     | 1 | Capture 1.2 (Timer1) |                      |

| 9:8     | P0.20    | 0     | 0 | GPIO Port 0.20       | 0                    |

|         |          | 0     | 1 | Match 1.3 (Timer1)   |                      |

|         |          | 1     | 0 | SSEL (SPI1)          |                      |

|         |          | 1     | 1 | EINT3                |                      |

Pin function select register 1 (PINSEL1 - 0xE002C004)...continued Table 7:

| PINSEL1 | Pin Name | Value |   | Function             | Value after |

|---------|----------|-------|---|----------------------|-------------|

|         |          |       |   |                      | Reset       |

| 11:10   | P0.21    | 0     | 0 | GPIO Port 0.21       | 0           |

|         |          | 0     | 1 | PWM5                 |             |

|         |          | 1     | 0 | Reserved             |             |

|         |          | 1     | 1 | Capture 1.3 (Timer1) |             |

| 13:12   | P0.22    | 0     | 0 | GPIO Port 0.22       | 0           |

|         |          | 0     | 1 | Reserved             |             |

|         |          | 1     | 0 | Capture 0.0 (Timer0) |             |

|         |          | 1     | 1 | Match 0.0 (Timer0)   |             |

| 15:14   | P0.23    | 0     | 0 | GPIO Port 0.23       | 0           |

|         |          | 0     | 1 | Reserved             |             |

|         |          | 1     | 0 | Reserved             |             |

|         |          | 1     | 1 | Reserved             |             |

| 17:16   | P0.24    | 0     | 0 | GPIO Port 0.24       | 0           |

|         |          | 0     | 1 | Reserved             |             |

|         |          | 1     | 0 | Reserved             |             |

|         |          | 1     | 1 | Reserved             |             |

| 19:18   | P0.25    | 0     | 0 | GPIO Port 0.25       | 0           |

|         |          | 0     | 1 | Reserved             |             |

|         |          | 1     | 0 | Reserved             |             |

|         |          | 1     | 1 | Reserved             |             |

| 21:20   | P0.26    | 0     | 0 | Reserved             | 0           |

|         |          | 0     | 1 | Reserved             |             |

|         |          | 1     | 0 | Reserved             |             |

|         |          | 1     | 1 | Reserved             |             |

| 23:22   | P0.27    | 0     | 0 | GPIO Port 0.27       | 1           |

|         |          | 0     | 1 | AIN0 (A/D input 0)   |             |

|         |          | 1     | 0 | Capture 0.1 (Timer0) |             |

|         |          | 1     | 1 | Match 0.1 (Timer0)   |             |

| 25:24   | P0.28    | 0     | 0 | GPIO Port 0.28       | 1           |

|         |          | 0     | 1 | AIN1 (A/D input 1)   |             |

|         |          | 1     | 0 | Capture 0.2 (Timer0) |             |

|         |          | 1     | 1 | Match 0.2 (Timer0)   |             |

| 27:26   | P0.29    | 0     | 0 | GPIO Port 0.29       | 1           |

|         |          | 0     | 1 | AIN2 (A/D input 2)   |             |

|         |          | 1     | 0 | Capture 0.3 (Timer0) |             |

|         |          | 1     | 1 | Match 0.3 (Timer0)   |             |

| 29:28   | P0.30    | 0     | 0 | GPIO Port 0.30       | 1           |

|         |          | 0     | 1 | AIN3 (A/D input 0)   |             |

|         |          | 1     | 0 | EINT3                |             |

|         |          | 1     | 1 | Capture 0.0 (Timer0) |             |

Table 7: Pin function select register 1 (PINSEL1 - 0xE002C004)...continued

| PINSEL1 | Pin Name | Value |   | Function | Value after<br>Reset |

|---------|----------|-------|---|----------|----------------------|

| 31:30   | P0.31    | 0     | 0 | Reserved | 0                    |

|         |          | 0     | 1 | Reserved |                      |

|         |          | 1     | 0 | Reserved |                      |

|         |          | 1     | 1 | Reserved | _                    |

# 6.9 Pin function select register 2 (PINSEL2 - 0xE002C014)

The PINSEL2 register controls the functions of the pins as per the settings listed in Table 8. The direction control bit in the IODIR register is effective only when the GPIO function is selected for a pin. For other functions direction is controlled automatically. Settings other than those shown in the table are reserved, and should not be used.

Table 8: Pin function select register 2 (PINSEL2 - 0xE002C014)

| PINSEL2 bits | Description                                        |                                   |                           | Reset value         |

|--------------|----------------------------------------------------|-----------------------------------|---------------------------|---------------------|

| 1:0          | Reserved.                                          |                                   |                           | -                   |

| 2            | When 0, pins P1.36:26<br>Debug port.               | are used as GPIO pins. When       | 1, P1.31:26 are used as a | P1.26/RTCK          |

| 3            | When 0, pins P1.25:16 Trace port.                  | are used as GPIO pins. When       | 1, P1.25:16 are used as a | P1.20/<br>TRACESYNC |

| 5:4          | Controls the use of the                            | data bus and strobe pins:         |                           | BOOT1:0             |

|              | Pins P2.7:0                                        | 11 = P2.7:0                       | 0x  or  10 = D7:0         |                     |

|              | Pin P1.0                                           | 11 = P1.0                         | 0x  or  10 = CS0          |                     |

|              | Pin P1.1                                           | 11 = P1.1                         | 0x  or  10 = OE           |                     |

|              | Pin P3.31                                          | 11 = P3.31                        | 0x  or  10 = BLS0         |                     |

|              | Pins P2.15:8 00                                    | or 11 = P2.15:8                   | 01 or 10 = D15:8          |                     |

|              | Pin P3.30 00                                       | or 11 = P3.30                     | 01 or 10 = BLS1           |                     |

|              | Pins P2.27:16 0x                                   | or 11 = P2.27:16                  | 10 = D27:16               |                     |

|              | Pins P2.29:28 0x                                   | or 11 = P2.29:28 or reserved      | 10 = D29:28               |                     |

|              | Pins P2.31:30 0x                                   | or 11 = P2.31:30 or AIN5:4        | 10 = D31:30               |                     |

|              | Pins P3.29:28 0x                                   | or 11 = P3.29:28 or AIN6:7        | 10 = BLS2:3               |                     |

| 6            | If bits 5:4 are not 10, co                         | ntrols the use of pin P3.29: 0 of | enables P3.29, 1 enables  | 1                   |

| 7            | If bits 5:4 are not 10, co                         | ntrols the use of pin P3.28: 0 of | enables P3.28, 1 enables  | 1                   |

| 8            | Controls the use of pin                            | P3.27: 0 enables P3.27, 1 ena     | bles WE.                  | 0                   |

| 10:9         | Reserved.                                          |                                   |                           | -                   |

| 11           | Controls the use of pin                            | P3.26: 0 enables P3.26, 1 ena     | bles CS1.                 | 0                   |

| 12           | Reserved.                                          |                                   |                           | -                   |

| 13           | If bits 25:23 are not 111<br>P3.23, 1 enables XCLK | , controls the use of pin P3.23   | A/A23/XCLK: 0 enables     | 0                   |

| 15:14        | Controls the use of pin are reserved values.       | P3.25: 00 enables P3.25, 01 e     | enables CS2, 10 and 11    | 00                  |

| 17:16        | Controls the use of pin are reserved values.       | P3.24: 00 enables P3.24, 01 e     | enables CS3, 10 and 11    | 00                  |

Table 8: Pin function select register 2 (PINSEL2 - 0xE002C014)...continued

| PINSEL2 bits | Description                                  |                                                       | Reset value           |

|--------------|----------------------------------------------|-------------------------------------------------------|-----------------------|

| 19:18        | Reserved.                                    |                                                       | -                     |

| 20           | If bits 5:4 are not 10, contro               | ols the use of pin P2.29:28: 0 enables P2.29:28, 1 is | 0                     |

| 21           | If bits 5:4 are not 10, contro               | ols the use of pin P2.30: 0 enables P2.30, 1 enables  | 1                     |

| 22           | If bits 5:4 are not 10, contro               | 1                                                     |                       |

| 23           | Controls whether P3.0/A0 i                   | 1 if BOOT1:0=00<br>at RESET=0,<br>0 otherwise         |                       |

| 24           | Controls whether P3.1/A1 i                   | s a port pin (0) or an address line (1).              | BOOT1 during<br>Reset |

| 27:25        | Controls the number of pinare address lines: | 000 if<br>BOOT1:0=11 at                               |                       |