# 带 31 字节非易失性静态 RAM 的串行实时时钟

## 特点

- 可对秒,分,时,日,周,月以及带闰年补偿 的年进行计数

- 用于高速数据暂存的 31 字节非易失性 RAM

- 宽工作电源电压范围: 2.0V~5.5V

- 2.5V 时耗电小于 300nA

- 用于时钟或 RAM 数据读/写的单字节或多字节数据传送方式

- 简单的3线接口与单片机通信

- TTL 兼容(V<sub>CC</sub>=5V)

- 可选的工业温度范围-40℃至+85℃

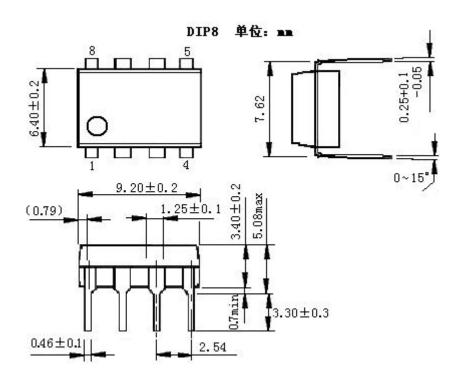

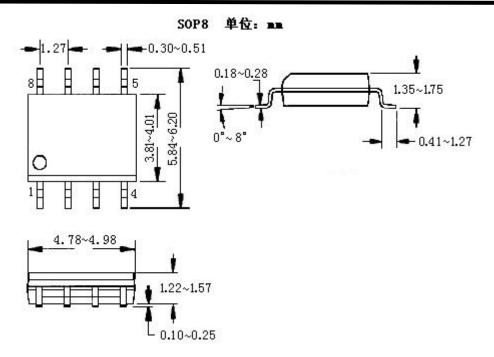

- 封装形式: DIP8 和 SOP8

# 应用

- 便携仪器

- 移动电话

- 复费率电度表、IC 卡水表、IC 卡煤气表

- 传真机

### 概述

DS1302 可慢速充电实时时钟芯片包含实时时钟/日历和 31 字节的非易失性静态 RAM。它经过一个简单的串行接口与微处理器通信。实时时钟/日历可对秒,分,时,日,周,月,和年进行计数,对于小于31 天的月,月末的日期自动进行调整,还具有闰年校正的功能。时钟可以采用 24 小时格式或带 AM(上午)/PM(下午)的 12 小时格式。31 字节的 RAM 可以用来临时保存一些重要数据。使用同步串行通信,简化了 DS1302 与微处理器的通信。与时钟/RAM 通信仅需 3 根线:(1)RST(复位),(2)I/O(数据线)和(3)SCLK(串行时钟)。数据可以以每次一个字节的单字节形式或多达 31 字节的多字节形式传输。DS1302能在非常低的功耗下工作,消耗小于 1 PW 的功率便能保存数据和时钟信息。

## 定购信息

| 器件       | 工作温度范围       | 封装类型 |

|----------|--------------|------|

| DS1302N  | 0°C∼+70°C    | DIP8 |

| DS1302M  | 00/27/00     | SOP8 |

| DS1302ZN | 40°C ~ 95°C  | DIP8 |

| DS1302ZM | -40°C ∼+85°C | SOP8 |

# 方框图和管脚功能

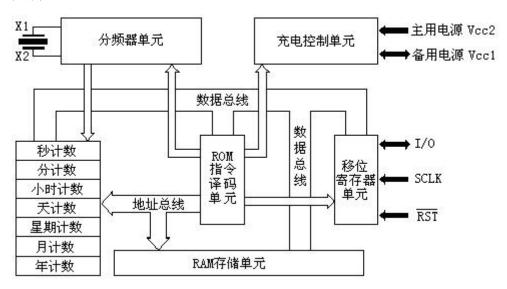

图 1 DS1302 内部框图

## 管脚说明

| 管脚序号 | 符号               | 功能           | 管脚序号 | 符号               | 功能      |

|------|------------------|--------------|------|------------------|---------|

| 1    | V <sub>CC2</sub> | 主用电源         | 5    | RST              | 复位      |

| 2    | X1               | 32.768kHz 晶体 | 6    | I/O              | 数据输入/输出 |

| 3    | X2               | 32.768kHz 晶体 | 7    | SCLK             | 串行时钟输入  |

| 4    | GND              | 地            | 8    | V <sub>CC1</sub> | 备用电源    |

# 最大额定值

| 参数名称   | 符号             | 测试条件 | 额定值       | 单位         |

|--------|----------------|------|-----------|------------|

| 引脚对地电压 | $V_P$          |      | -0.5∼+7.0 | V          |

| 工作温度   | T <sub>A</sub> |      | 0∼70      | $^{\circ}$ |

| 贮存温度   | Ts             |      | -55∼+125  | $^{\circ}$ |

| 焊接温度   | T <sub>H</sub> |      | 260(10 秒) | $^{\circ}$ |

## 推荐直流运行条件(T<sub>A</sub>=0℃~70℃)

| 参数名称      | 符号                    | 测试条件     | 最小值  | 典型值 | 最大值                  | 单位 |

|-----------|-----------------------|----------|------|-----|----------------------|----|

| 供给电源电压    | $V_{CC1}$ , $V_{CC2}$ |          | 2.0  |     | 5.5                  | V  |

| 逻辑 1 输入电压 | V <sub>IH</sub>       |          | 2.0  |     | V <sub>cc</sub> +0.3 | V  |

| 逻辑 0 输入电压 | V                     | VCC=2.0V | -0.3 |     | +0.3                 | V  |

| 2         | V <sub>IL</sub>       | VCC=5V   | -0.3 |     | +0.8                 | V  |

## 电容(T<sub>A</sub>=25℃)

| 参数名称    | 符号               | 测试条件 | 最小值 | 典型值 | 最大值 | 单位 |

|---------|------------------|------|-----|-----|-----|----|

| 输入电容    | Cı               |      |     | 10  |     | pF |

| I/O 电容  | C <sub>I/O</sub> |      |     | 15  |     | pF |

| 晶体振荡器电容 | C <sub>X</sub>   |      |     | 6   |     | pF |

# 电特性

# **直流电特性** (0℃至 70℃; V<sub>∞</sub>=2.5V 至 5.5V)

| 参数名称             | 符号                | 测试条件                   | 最小值 | 典型值 | 最大值   | 单位 |

|------------------|-------------------|------------------------|-----|-----|-------|----|

| 输入电流             | Lu                |                        |     |     | 500   | μА |

| I/O 漏电流          | I <sub>LO</sub>   |                        |     |     | 500   | μА |

| 逻辑 1 输出电压        | V                 | V <sub>CC</sub> =2.5V  | 1.6 |     |       | V  |

| 炒拇 ▮ 棚田电压        | V <sub>OH</sub>   | V <sub>CC</sub> =5V    | 2.4 |     |       | V  |

| <b>逻辑 o</b> 於山由耳 | V                 | V <sub>CC</sub> =2.5V  |     |     | 0.4   | V  |

| 逻辑 0 输出电压        | V <sub>OL</sub>   | V <sub>CC</sub> =5V    |     |     | 0.4   | V  |

| 供由由法             | 1                 | V <sub>CC1</sub> =2.5V |     |     | 0.4   | A  |

| 供电电流             | I <sub>CC1A</sub> | V <sub>CC1</sub> =5V   |     |     | 1.2   | mA |

| 叶间伊牡山沟           | 1                 | V <sub>CC1</sub> =2.5V |     |     | 0.3   | A  |

| 时间保持电流           | I <sub>CC1T</sub> | V <sub>CC1</sub> =5V   |     |     | 1     | μА |

| <b> </b>         |                   | V <sub>CC1</sub> =2.5V |     | 100 |       | nA |

| 静态电流             | I <sub>CC1S</sub> | V <sub>CC1</sub> =5V   |     | 100 |       |    |

| 供由由法             |                   | V <sub>CC2</sub> =2.5V |     |     | 0.425 | mA |

| 供电电流             | I <sub>CC2A</sub> | V <sub>CC2</sub> =5V   |     |     | 1.28  |    |

| 叶词伊牡山沟           |                   | V <sub>CC2</sub> =2.5V |     |     | 25.3  | Л  |

| 时间保持电流           | I <sub>CC2T</sub> | V <sub>CC2</sub> =5V   |     |     | 81    | μА |

| <b>热大</b> 山达     |                   | V <sub>CC2</sub> =2.5V |     |     | 25    | Л  |

| 静态电流             | I <sub>CC2S</sub> | V <sub>CC2</sub> =5V   |     |     | 80    | μА |

|                  | R1                |                        |     | 2   |       |    |

| 涓流充电电阻           | R2                |                        |     | 4   |       | kΩ |

|                  | R3                |                        |     | 8   |       |    |

| 涓流充电二极管<br>压降    | V <sub>TD</sub>   |                        |     | 0.7 |       | V  |

# **交流电特性**(T<sub>A</sub>=0℃至 70℃; V<sub>CC</sub>=+5V±10%)

| ~ · · · · · · · · · · · · · · · · · · · | · · · · · · · · · · · · · · · · · · |                       |     |     |     |    |

|-----------------------------------------|-------------------------------------|-----------------------|-----|-----|-----|----|

| 参数名称                                    | 符号                                  | 测试条件                  | 最小值 | 典型值 | 最大值 | 单位 |

| CLK 到 RST 保持                            |                                     | V <sub>CC</sub> =2.5V | 240 |     |     |    |

| CLK 到 KSI 体行                            | t <sub>cch</sub>                    | V <sub>CC</sub> =5V   | 60  |     |     | ns |

| PCT T☆b                                 | t <sub>cwh</sub>                    | V <sub>CC</sub> =2.5V | 4   |     |     |    |

| RST 无效                                  |                                     | V <sub>CC</sub> =5V   | 1   |     |     | ns |

| RST 到 I/O 高阻                            | +                                   | V <sub>CC</sub> =2.5V |     |     | 280 | nc |

| KSI 到 I/U 同阻                            | t <sub>cdz</sub>                    | V <sub>CC</sub> =5V   |     |     | 70  | ns |

| SCLK 到 I/O 高阻                           | t <sub>ccz</sub>                    | V <sub>CC</sub> =2.5V |     |     | 280 | ns |

|                            |                                 | V <sub>CC</sub> =5V   |      | 70   |         |

|----------------------------|---------------------------------|-----------------------|------|------|---------|

| Data 到 CLK 建立              |                                 | V <sub>CC</sub> =2.5V | 200  |      |         |

| Data 到 CLK 建立              | t <sub>dc</sub>                 | V <sub>CC</sub> =5V   | 50   |      | ns      |

| CIV Al Data 但性             |                                 | V <sub>CC</sub> =2.5V | 280  |      |         |

| CLK 到 Data 保持              | t <sub>cdh</sub>                | V <sub>CC</sub> =5V   | 70   |      | ns      |

| CLV ZII Data 77 III        | 1                               | V <sub>CC</sub> =2.5V |      | 800  |         |

| CLK 到 Data 延时              | t <sub>cdd</sub>                | V <sub>CC</sub> =5V   |      | 200  | ns      |

| CLV (IT                    | l t <sub>cl</sub> ⊢             | V <sub>CC</sub> =2.5V | 1000 |      | ns      |

| CLK 低                      |                                 | V <sub>CC</sub> =5V   | 250  |      |         |

| CLK 高                      |                                 | V <sub>CC</sub> =2.5V | 1000 |      |         |

| CLK 向                      | t <sub>ch</sub>                 | V <sub>CC</sub> =5V   | 250  |      | ns      |

| CLK 频率                     | _                               | V <sub>CC</sub> =2.5V |      | 0.5  | N 41.1- |

| CLK 妙孚                     | t <sub>clk</sub>                | V <sub>CC</sub> =5V   | DC   | 2.0  | MHz     |

| CLK 上升和下将 t <sub>r</sub> , |                                 | V <sub>CC</sub> =2.5V |      | 2000 |         |

|                            | t <sub>r</sub> , t <sub>f</sub> | V <sub>CC</sub> =5V   |      | 500  | ns      |

| pct 죄 CLV 계수               | 1                               | V <sub>CC</sub> =2.5V | 4    |      | 11-     |

| RST 到 CLK 建立               | t <sub>cc</sub>                 | V <sub>cc</sub> =5V   | 1    |      | μς      |

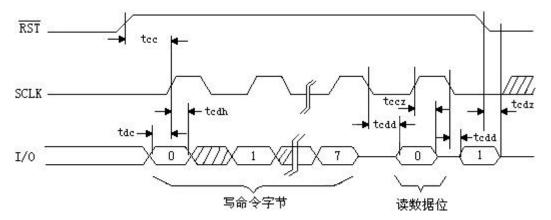

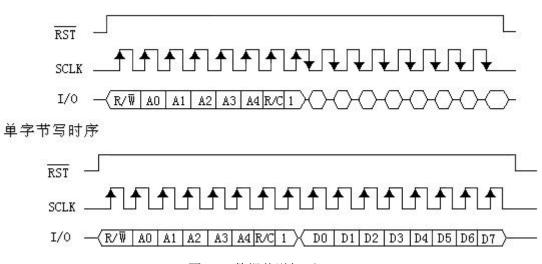

## 时序图: 读数据

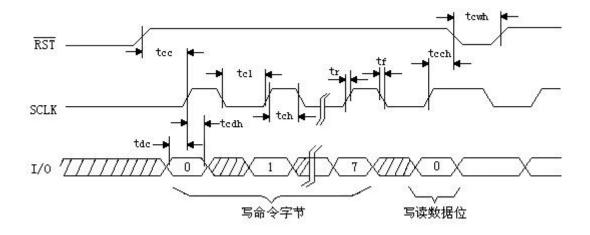

时序图:写数据

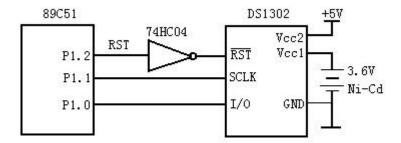

# 典型应用电路图

### 使用说明:

串行时钟芯片的主要组成部分示于图 1:移位寄存器控制逻辑,振荡器,实时时钟以及 RAM。

工作原理:如图所示,RST信号有效后,移位寄存器单元会在 SCLK 同步脉冲信号的控制下从 I/O 上串行接收 8 位指令字节,然后将 8 位指令字节进行串并转换并送至 ROM 指令译码单元。由 ROM 指令译码单元对 8 位指令字节进行译码,以决定内部寄存器的地址以及读写状态。然后在接下来的 SCLK 同步脉冲信号的控制下将 8 位数据写进或者读出相应的寄存器。数据传送也可以采用多字节方式,先将 8 位相应的指令字节写入,然后在连续的 SCLK 的脉冲信号同步下,将数据字节连续写入或读出日历/时钟寄存器(或者RAM 单元)。SCLK 脉冲的个数在单字节方式下为 8 加 8,在多字节方式下为 8 加最大可达到 248 的数。

### 1、命令字节

命令字节示于图 2:每一数据传送由命令字节初始化,最高有效位 MSB(位 7)必须为逻辑 1。如果它是零,禁止写 DS1302。位 6 为逻辑 0 指定时钟/日历数据。逻辑 1 指定 RAM 数据。位 1 至 5 指定进行输入或输出的特定寄存器。最低有效位 LSB(位 0)为逻辑 0 指定进行写操作(输入);逻辑 1 指定进行读操作(输出)。命令字节总是从最低有效 LSB 位 0 开始输入。

| 1 | RAM/CLK | A4 | A3 | A2 | A1 | A0 | 读/写 |

|---|---------|----|----|----|----|----|-----|

|---|---------|----|----|----|----|----|-----|

图 2 地址/命令字节

#### 2、复位和时钟控制

通过把 RST 输入驱动至高电平来启动所有的数据传送。RST 输入有两种功能。首先,RST 接通控制逻辑,允许地址命令序列送入移位寄存器。其次,RST 可以中止数据传送。数据输入时,在时钟的上升沿数据必须有效,而数据位在时钟的下降沿输出。如果 RST 输入为低电平,那么所有的数据传送中止,且 I/O 引脚变为高阻。数据传送在图 3 中说明。上电时,在 VCC 大于或等于 2.5V 之前,RST 必须为逻辑 0,此外,当把 RST 驱动至逻辑 1 的状态时,SCLK 必须为逻辑 0。

#### 3、数据输入

跟随在输入写命令字节的 8 个 SCLK 周期之后,在下 8 个 SCLK 周期的上升沿输入数据。如果有额外的 SCLK 周期,它们将被忽略。输入从位 0 开始。

#### 4、数据输出

跟随在输入读命令字节的 8 个 SCLK 周期之后,在随后的 8 个 SCLK 周期的下降沿输出数据字节。注意,被传送的每一个数据位发生在读命令字节的最后一位之后的第一个下降沿。只要 RST 保持为高电平,如果有额外的 SCLK 周期,它们将重新发送数据字节。这一操作使之具有连续的多字节方式的读能力。另外,在 SCLK 的每一个上升沿,I/O 引脚为三态。数据从位 0 开始输出。

#### 5、多字节方式

通过对 31(十进制)位地址寻址(地址/命令位于 1 至 5=逻辑 1),可以把时钟/日历或 RAM 寄存器规定为 多字节方式。如前所述,位 6 规定时钟或 RAM 而位 0 规定读或写。在时钟\日历寄存器中的地址 9 至 31 或 RAM 寄存器中的地址 31 不能存储数据。在多字节方式中读或写从地址 0 的位 0 开始。当以多字节方式 写时钟寄存器时,必须按数据传送的次序写最先 8 个寄存器。但是,当以多字节方式写 RAM 时,为了传送数据不必写所有 31 个字节。不管是否写了全部 31 个字节,所写的每一个字节都将传送至 RAM。

| 功能    | 字节数 | 脉冲数 |

|-------|-----|-----|

| CLOCK | 8   | 72  |

| RAM   | 31  | 256 |

### 单字节读时序

图 3 数据传送概要

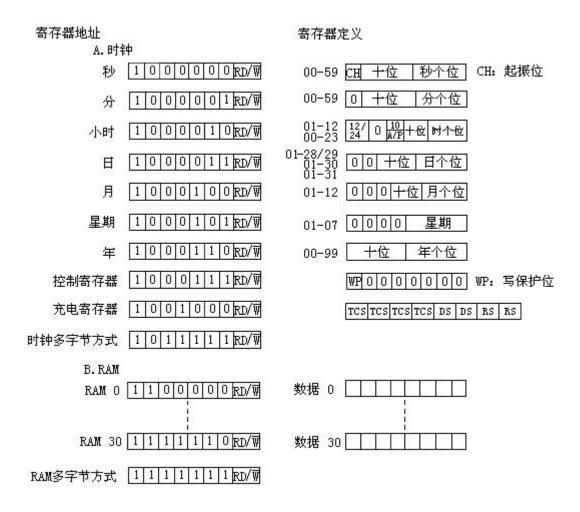

#### 6、时钟/日历

如图 4 所示,时钟/日历包含在 7 个写/读寄存器内。包含在时钟/日历寄存器内的数据是二一十进制 (BCD) 码。

#### 7、时钟暂停

秒寄存器的位 7 定义为时钟暂停位。当此位设置为逻辑 1 时,时钟振荡器停止,DS1302 被置入低功率的备份方式,其电源消耗小于 100 纳安(nanoamp)。当把此位写成逻辑 0 时,时钟将启动。

#### 8、AM-PM/12-24 方式

小时寄存器的位 7 定义为 12 或 24 小时方式选择位。当它为高电平时,选择 12 小时方式,在 12 小时方式下,位 5 是 AM/PM 位,此位为逻辑高电平表示 PM。在 24 小时方式下,位 5 是第 2 个 10 小时位(20-23 时)。

#### 9、写保护寄存器

写保护寄存器的位7是写保护位。开始7位(位0-6)置为零,在读操作时总是读出零。在对时钟或

RAM 进行写操作之前,位7必须为零。当它为高电平时,写保护位禁止对任何其它寄存器进行写操作。

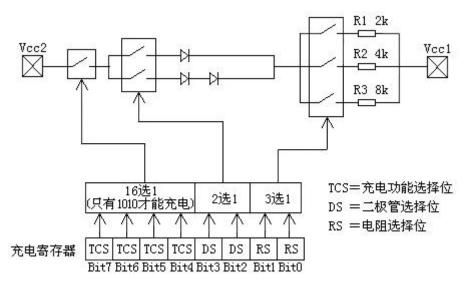

### 10、慢速充电(Trickle charge)寄存器

这个寄存器控制 DS1302 的慢速充电特性。图 4 的简化电路表示慢速充电器的基本组成。慢速充电选择(TCS)位(位 4-7)控制慢速充电器的选择。为了防止偶然的因素使之工作,只有 1010 模式才能使慢速充电器工作,所有其它的模式将禁止慢速充电器。DS1302 上电时,慢速充电器被禁止。二极管选择(DS)位(位 2-3)选择是一个二极管还是两个二极管连接在 Vcc2 与 Vcc1 之间。如果 DS 为 01,那么选择一个二极管;如果 DS 为 10,则选择两个二极管。如果 DS 为 00 或 11,那么充电器被禁止,与 TCS 无关。RS 位(位 0-1)选择连接在 Vcc2 与 Vcc1 之间的电阻。电阻选择(RS)位选择的电阻如下:

| RS位 | 电阻器  | 典型值 |

|-----|------|-----|

| 00  | 无    | 无   |

| 01  | R1   | 2kΩ |

| 10  | . R2 | 4kΩ |

| 11  | R3   | 8kΩ |

图 4 DS1302 可编程慢速充电器

如果 RS 为 00, 充电器被禁止, 与 TCS 无关。

二极管和电阻的选择用户根据电池和超容量电容充电所需的最大电流决定。最大充电电流可以如下列 所说明的那样进行计算。假定 5V 系统电源加到 Vcc2 而超容量电容接至 Vcc1。再假设慢速充电器工作时在 Vcc2 和 Vcc1 之间接有一个二极管和电阻 R1。因而最大电流可计算如下:

> Imax = (5.0V-二极管压降)/R1 = (5.0V-0.7V) /2k $\Omega$ = 2.2mA

显而易见, 当超容量电容充电时, Vcc2 和 Vcc1 之间的电压减少, 因而充电电流将会减小。

## 11、时钟/日历多字节(Burst)方式

时钟/日历命令字节可规定多字节工作方式。在此方式下,最先8个时钟/日历寄存器可以从地址0的第0位开始连续地读或写(见图4)。

当指定写时钟/日历的多字节方式时,如果写保护位设置为高电平,那么没有数据会传到8个时钟/日历寄存器(包括控制寄存器)中的任一个。在多字节方式下,慢速充电器时不可访问的。

#### 12 RAM

静态 RAM 是 RAM 地址空间中顺序寻址的 31×8 字节。

### 13、RAM 多字节方式

RAM 命令字节可规定多字节工作方式。在此方式下,可以从地址 0 的第 0 位开始顺序读或写 31 字节 RAM 寄存器(见图 5)。

### 14、寄存器概要

寄存器数据格式概要示于图 5.

图 5 寄存器地址/定义

### 15、晶振选择

**32.768kHz** 的晶振可通过引脚 2 和 3 (X1 和 X2) 直接连接至 DS1302。所选晶振规定的负载电容量 (CL) 应当为 6pF。

### 16、电源控制

Vcc1 在单电源与电池供电的系统中提供低电源并提供低功率的电池备份。

Vcc2 在双电源系统中提供主电源,此时 Vcc1 连接到备份电源,以便在没有主电源的情况下能保存时间信息以及数据。

DS1302 由 Vcc1 或 Vcc2 两者中较大者供电。当 Vcc2 大于 Vcc1+0.2V 时,DS1302 由 Vcc2 供电。当 Vcc2+0.2V 小于 Vcc1 时,DS1302 由 Vcc1 供电。

# 封装尺寸

## 重要声明:

华冠半导体保留未经通知更改所提供的产品和服务。客户在订货前应获取最新的相关信息,并核实这些信息是否最新且完整的。

客户在使用华冠半导体产品进行系统设计和整机制造时有责任遵守安全标准并采取安全措施,以避免潜在风险可能导致人身伤害或财产损失情况的发生。

华冠半导体产品未获得生命支持、军事、航空航天等领域应用之许可,华冠半导体将不承担产品在这些领域应用造成的后果。

华冠半导体的文档资料,仅在没有对内容进行任何篡改且带有相关授权的情况下才允许进行复制。华冠半导体对篡改过的文件不承担任何责任或义务。